# X20DC1976

Data sheet 2.35 (October 2024)

#### **Publishing information**

B&R Industrial Automation GmbH B&R Strasse 1 5142 Eggelsberg Austria

Telephone: +43 7748 6586-0

Fax: +43 7748 6586-26

office@br-automation.com

#### Disclaimer

All information in this document is current as of its creation. The contents of this document are subject to change without notice. B&R Industrial Automation GmbH assumes unlimited liability in particular for technical or editorial errors in this document only (i) in the event of gross negligence or (ii) for culpably inflicted personal injury. Beyond that, liability is excluded to the extent permitted by law. Liability in cases in which the law stipulates mandatory unlimited liability (such as product liability) remains unaffected. Liability for indirect damage, consequential damage, business interruption, loss of profit or loss of information and data is excluded, in particular for damage that is directly or indirectly attributable to the delivery, performance and use of this material.

B&R Industrial Automation GmbH notes that the software and hardware designations and brand names of the respective companies used in this document are subject to general trademark, brand or patent protection.

Hardware and software from third-party suppliers referenced in this document is subject exclusively to the respective terms of use of these third-party providers. B&R Industrial Automation GmbH assumes no liability in this regard. Any recommendations made by B&R Industrial Automation GmbH are not contractual content, but merely non-binding information for which no liability is assumed. When using hardware and software from third-party suppliers, the relevant user documentation of these third-party suppliers must additionally be consulted and, in particular, the safety guidelines and technical specifications contained therein must be observed. The compatibility of the products from B&R Industrial Automation GmbH described in this document with hardware and software from third-party suppliers is not contractual content unless this has been separately agreed in individual cases; in this respect, warranty for such compatibility is excluded in any case, and it is the sole responsibility of the customer to verify this compatibility in advance.

#### **Version history**

B&R makes every effort to keep documents as current as possible. The most current versions are available for download on the B&R website (www.br-automation.com).

## 1 General information

## 1.1 Other applicable documents

For additional and supplementary information, see the following documents.

#### Other applicable documents

| Document name | Title                    |

|---------------|--------------------------|

| MAX20         | X20 System user's manual |

#### 1.2 Order data

Table 1: X20DC1976 - Order data

## 1.3 Module description

The module is equipped with 1 input for an ABR incremental encoder with 5 V encoder supply. The encoder inputs are monitored (A, B, R). The module is suitable for incremental encoders with push-pull outputs with no complementary signal.

#### **Functions:**

- ABR incremental encoder

- Monitoring signal lines

- · Monitoring the encoder power supply

- NetTime Technology

#### **ABR** incremental encoder

The module provides 1 input for ABR incremental encoders. This allows the detection of position (linear) or angular (rotating) changes in ABR encoders.

#### Monitoring status of channels

All channels can be monitored for an open circuit, short circuit or low voltage levels.

## Monitoring the supply voltage

The encoder power supply voltage is monitored.

#### NetTime timestamp of the counter

For many applications, not only the counter value is important, but also the exact time of the counter change. For this purpose, the module has a NetTime function that provides the recorded counter value with a timestamp accurate to microseconds.

# 2 Technical description

## 2.1 Technical data

| Order number                                                     | X20DC1976                                                                                                                                 |

|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Short description                                                |                                                                                                                                           |

| I/O module                                                       | 1 ABR incremental encoder 5 V                                                                                                             |

| General information                                              |                                                                                                                                           |

| B&R ID code                                                      | 0xA707                                                                                                                                    |

| Status indicators                                                | I/O function per channel, operating state, module status                                                                                  |

| Diagnostics                                                      |                                                                                                                                           |

| Module run/error                                                 | Yes, using LED status indicator and software                                                                                              |

| Power consumption                                                |                                                                                                                                           |

| Bus                                                              | 0.01 W                                                                                                                                    |

| Internal I/O                                                     | 1.2 W                                                                                                                                     |

| Additional power dissipation caused by actuators (resistive) [W] | -                                                                                                                                         |

| Type of signal lines                                             | Shielded lines must be used for all signal lines.                                                                                         |

| Certifications                                                   |                                                                                                                                           |

| CE                                                               | Yes                                                                                                                                       |

| UKCA                                                             | Yes                                                                                                                                       |

| ATEX                                                             | Zone 2, II 3G Ex nA nC IIA T5 Gc<br>IP20, Ta (see X20 user's manual)<br>FTZÚ 09 ATEX 0083X                                                |

| UL                                                               | cULus E115267<br>Industrial control equipment                                                                                             |

| HazLoc                                                           | cCSAus 244665 Process control equipment for hazardous locations Class I, Division 2, Groups ABCD, T5                                      |

| DNV                                                              | Temperature: <b>B</b> (0 to 55°C)<br>Humidity: <b>B</b> (up to 100%)<br>Vibration: <b>B</b> (4 g)<br>EMC: <b>B</b> (bridge and open deck) |

| CCS                                                              | Yes                                                                                                                                       |

| LR                                                               | ENV1                                                                                                                                      |

| KR                                                               | Yes                                                                                                                                       |

| ABS                                                              | Yes                                                                                                                                       |

| BV                                                               | <b>EC33B</b><br>Temperature: 5 - 55°C<br>Vibration: 4 g<br>EMC: Bridge and open deck                                                      |

| KC                                                               | Yes                                                                                                                                       |

| Digital inputs                                                   |                                                                                                                                           |

| Quantity                                                         | 2                                                                                                                                         |

| Nominal voltage                                                  | 24 VDC                                                                                                                                    |

| Input characteristics per EN 61131-2                             | Type 1                                                                                                                                    |

| Input voltage                                                    | 24 VDC -15% / +20%                                                                                                                        |

| Input current at 24 VDC                                          | Approx. 3.3 mA                                                                                                                            |

| Input circuit                                                    | Sink                                                                                                                                      |

| Input filter                                                     |                                                                                                                                           |

| Hardware                                                         | ≤2 µs                                                                                                                                     |

| Software                                                         | -                                                                                                                                         |

| Connection type                                                  | 3-wire connections                                                                                                                        |

| Input resistance                                                 | 7.03 kΩ                                                                                                                                   |

| Additional functions                                             | Latch input                                                                                                                               |

| Switching threshold                                              |                                                                                                                                           |

| Low                                                              | <5 VDC                                                                                                                                    |

| High                                                             | >15 VDC                                                                                                                                   |

| Insulation voltage between channel and bus                       | 500 V <sub>eff</sub>                                                                                                                      |

| ABR incremental encoder                                          |                                                                                                                                           |

| Encoder inputs                                                   | 5 V, asymmetrical                                                                                                                         |

| Counter size                                                     | 16/32-bit                                                                                                                                 |

|                                                                  |                                                                                                                                           |

| Input frequency                                                  | Max. 250 kHz                                                                                                                              |

| Input frequency Evaluation                                       | Max. 250 kHz  4x                                                                                                                          |

| Evaluation                                                       |                                                                                                                                           |

|                                                                  | 4x                                                                                                                                        |

| Evaluation Minimum diff. slew rate                               | 4x                                                                                                                                        |

Table 2: X20DC1976 - Technical data

| Order number                                   | X20DC1976                                           |

|------------------------------------------------|-----------------------------------------------------|

| Input filter                                   |                                                     |

| Hardware                                       | ≤600 ns                                             |

| Software                                       | -                                                   |

| Switching threshold                            |                                                     |

| Low                                            | >1 V                                                |

| Overload characteristics of encoder power sup- | Short-circuit proof, overload-proof                 |

| ply                                            |                                                     |

| Insulation voltage between encoder and bus     | 500 V <sub>eff</sub>                                |

| Electrical properties                          |                                                     |

| Electrical isolation                           | Channel isolated from bus                           |

|                                                | Channel not isolated from channel                   |

| Operating conditions                           |                                                     |

| Mounting orientation                           |                                                     |

| Horizontal                                     | Yes                                                 |

| Vertical                                       | Yes                                                 |

| Installation elevation above sea level         |                                                     |

| 0 to 2000 m                                    | No limitation                                       |

| >2000 m                                        | Reduction of ambient temperature by 0.5°C per 100 m |

| Degree of protection per EN 60529              | IP20                                                |

| Ambient conditions                             |                                                     |

| Temperature                                    |                                                     |

| Operation                                      |                                                     |

| Horizontal mounting orientation                | -25 to 60°C                                         |

| Vertical mounting orientation                  | -25 to 50°C                                         |

| Derating                                       | -                                                   |

| Storage                                        | -40 to 85°C                                         |

| Transport                                      | -40 to 85°C                                         |

| Relative humidity                              |                                                     |

| Operation                                      | 5 to 95%, non-condensing                            |

| Storage                                        | 5 to 95%, non-condensing                            |

| Transport                                      | 5 to 95%, non-condensing                            |

| Mechanical properties                          |                                                     |

| Note                                           | Order 1x terminal block X20TB12 separately.         |

|                                                | Order 1x bus module X20BM11 separately.             |

| Pitch                                          | 12.5 <sup>+0.2</sup> mm                             |

Table 2: X20DC1976 - Technical data

## 2.2 LED status indicators

For a description of the various operating modes, see section "Additional information - Diagnostic LEDs" in the X20 System user's manual.

| Figure      | LED   | Color | Status       | Description                                                                                                                                                                                                                                                     |

|-------------|-------|-------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | r     | Green | Off          | No power to module                                                                                                                                                                                                                                              |

|             |       |       | Single flash | RESET mode                                                                                                                                                                                                                                                      |

|             |       |       | Double flash | BOOT mode (during firmware update) <sup>1)</sup>                                                                                                                                                                                                                |

|             |       |       | Blinking     | PREOPERATIONAL mode                                                                                                                                                                                                                                             |

|             |       |       | On           | RUN mode                                                                                                                                                                                                                                                        |

|             | е     | Red   | Off          | No power to module or everything OK                                                                                                                                                                                                                             |

| 9261 DO 023 |       |       | Single flash | The encoder monitor has detected a line fault on the encoder inputs. The status bits must be evaluated in order to provide a more detailed definition of this error. The following error states are detected:  Open line Short-circuit or voltage level too low |

| ~           |       |       | On           | Error or reset status                                                                                                                                                                                                                                           |

|             | A1    | Green |              | Input state of counter input A                                                                                                                                                                                                                                  |

|             | B1    | Green |              | Input state of counter input B                                                                                                                                                                                                                                  |

|             | R1    | Green |              | Input state of reference pulse R                                                                                                                                                                                                                                |

|             | 1 - 2 | Green |              | Input state of the corresponding digital input                                                                                                                                                                                                                  |

<sup>1)</sup> Depending on the configuration, a firmware update can take up to several minutes.

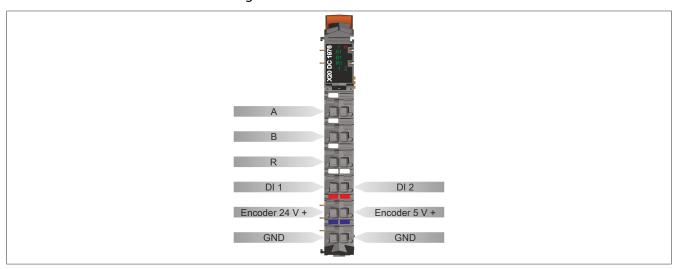

## 2.3 Pinout

Shielded cables must be used for all signal lines.

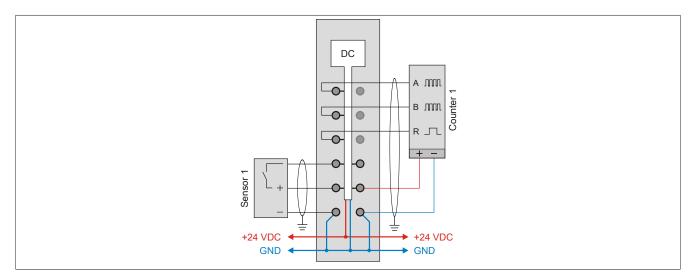

## 2.4 Connection example

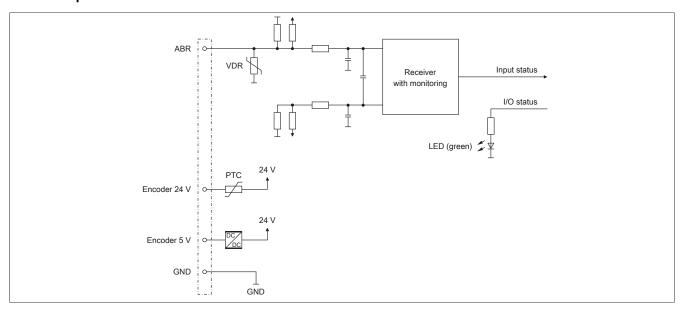

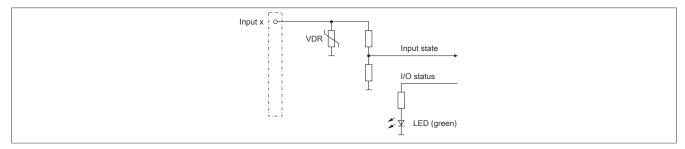

## 2.5 Input circuit diagram

## **Counter inputs**

#### **Standard inputs**

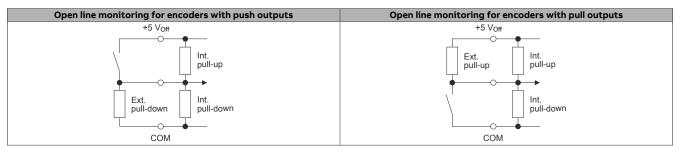

## 2.6 Open line monitoring

For encoders with push or pull outputs, open-circuit monitoring is only possible if the encoder itself is wired with pull-up or pull-down resistors (pull-up: Max. 2 k $\Omega$ , pull-down: Max. 560  $\Omega$ ).

## **3 Function description**

#### 3.1 ABR incremental encoder

This module is equipped with 1 input for ABR incremental encoders with output signals in accordance with RS422.

#### 3.1.1 General information

Incremental encoders are sensors for detecting position (linear) or angular (rotating) changes, which can detect distance and direction of travel or an angular change and direction of rotation.

In contrast to continuously operating measuring systems such as servo-potentiometers, incremental encoders have a measurement scale with repeating periodic graduation lines. The measurement is based on the direction determined and a count. Rotating optical encoders are the most commonly used.

Incremental encoders (in contrast to absolute encoders) may need to be referenced after switching on, as changes in position are not detected when in the switched-off state.

Typical applications are determining position and speed in automation technology.

#### 3.1.2 Signal evaluation

When a movement is performed, the two sensors emit 2 signals (A and B) with an electrical phase shift of 90°.

The module determines the direction from these 2 signals and counts the pulses. This allows direct conclusions to be drawn about the scale of measurement (path or angle).

#### 3.1.3 Referencing

After switching on the power supply, the incremental encoder only measures changes compared to the switch-on position. For many applications however, knowledge of the absolute position is required. For this reason, most angular encoders output a one reference pulse (zero pulse, reference mark) per revolution on a third output (reference signal R). After switching on, the encoder must be turned until the reference pulse has been detected. The absolute angle is then available after one revolution at the latest.

Positioning systems with incremental encoders perform so-called reference runs to an external position sensor (e.g. limit switch) after switching on. From this point, the next reference pulse of the incremental encoder is used as an accurate reference point.

#### 3.1.4 Recording the counter value

The counter value of the incremental encoder is displayed as a 16- or 32-bit counter value. The counter value can be reset if necessary. The counter is held at zero until the reset command is canceled.

#### 3.1.5 Latching counter values

If required, the current counter values can be latched.

To use the latch function, the latch mode and the signal channels for triggering the latch procedure must be configured:

#### Latch mode

- Configuring one-time (single-shot) latch mode:

The latch function must be enabled/set. After successful latching, which is indicated by the latch event counter, enabling must first be reset or no further latching is possible. If additional latching is desired, enabling must be set again.

- Configuring continuous latch mode:

The latch function must be enabled/set only as long as latching is desired. The latch event counter counts each event.

#### Signal channels

- This configuration determines which channels are linked to create the latch event. All 3 signals of the encoder and digital input 1 can be used for the "AND" operator.

- To adapt to the physical signals, the "active voltage level" required for the latch procedure can be defined as "High" or "Low".

#### Information:

The registers are described in "Counter and latch" on page 21.

## 3.2 Monitoring signal lines

Error monitoring must be individually enabled for each signal channel. An open circuit, short circuit or low voltage levels are reported as an error state. Any errors that occur are reported in the error status registers. When they occur, the error states are latched and remain so until an acknowledgment is received. If an error is still pending however, the error state remains active. After successful acknowledgment, however, the acknowledgment register bits must be reset. Otherwise, a new error will not be detected.

The error states can be acknowledged both manually as well as automatically.

#### **Automatic time specification**

In addition, the error state can be switched on using a time specification during automatic acknowledgment. If a valid time is set, manual acknowledgment is still possible, but automatic acknowledgment in the module is also triggered after the specified time has elapsed. If the error state has not been corrected, the error state remains pending and the time is restarted. It is important to ensure that the time specification is configured long enough to allow the primary system to reliably detect the status messages. If the time specification = 0, acknowledgment is only possible with the cyclic acknowledgment registers.

#### Information:

The registers are described in "Signal line error states" on page 23.

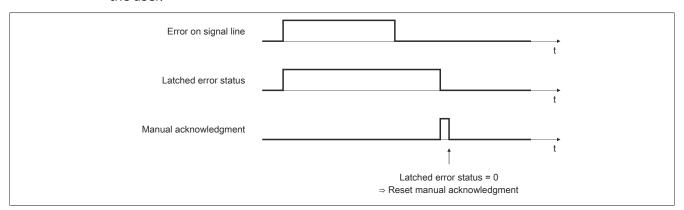

## 3.2.1 Manual acknowledgment of latched error states

The latched error states of the signal lines from the encoder can be acknowledged manually. However, if there are still pending errors remaining, then the error status remains active. After successfully acknowledging the errors (latched error status = 0), the acknowledge bits must still be reset by the user or else a re-occurrence of an error could be overlooked by the user.

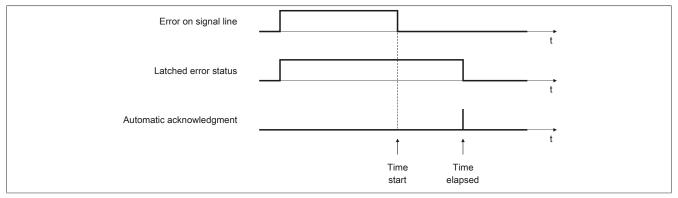

#### Example 1: Cause of error corrected before being acknowledged

An error has occurred on a signal line. The error state is detected and latched by the module. The error is acknowledged by the user after the cause of error has been corrected. The latched error status changes to zero.

The manual acknowledge must now be reset so that any new errors will be recognized by the user.

Figure 1: Cause of error corrected before being acknowledged

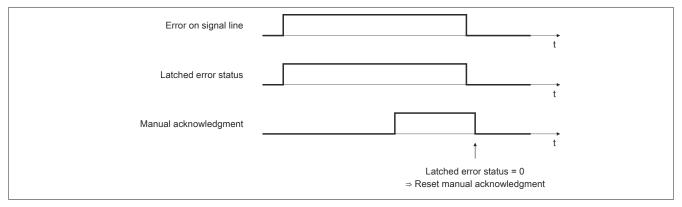

#### Example 2: Cause of error not yet corrected before being acknowledged

An error has occurred on a signal line. The error state is detected and latched by the module. The error is acknowledged by the user before the cause of error has been corrected. The latched error status remains set because the error is still remaining.

Acknowledgment is only successful after the cause of error has been corrected. The latched error status changes to zero. The manual acknowledge must now be reset so that any new errors will be recognized by the user.

Figure 2: Cause of error not yet corrected before being acknowledged

#### 3.2.2 Automatic acknowledgment of latched error states

In addition to manual acknowledgment, automatic AcknowledgeImage of the latched error states can be switched on using a time setting. It is important to note that the time specification is configured long enough so that the higher-level system can reliably recognize the status messages or that the validity of the counter value can be reliably determined via the age.

If the time specification = 0, then only manual acknowledgment is possible.

Example 1: An error has occurred on a signal line. The error state is detected and latched by the module. The time for automatic acknowledgment starts counting after the cause of error has been corrected. The error is acknowledged as soon as the time expires. The latched error status changes to zero.

Figure 3: Latched error state acknowledged automatically

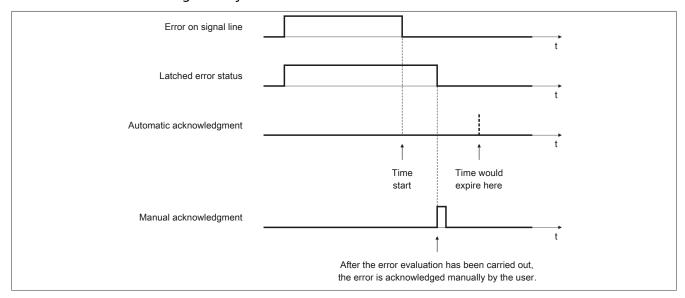

#### Example 2: Automatic and manual acknowledge used

An error has occurred on a signal line. The error state is detected and latched by the module. The time for automatic acknowledgment starts counting after the cause of error has been corrected.

The error is acknowledged manually by the user before the time expires. The latched error status changes to zero. The manual acknowledge must now be reset so that any new errors will be recognized by the user.

Figure 4: Automatic and manual acknowledge used

## 3.3 Monitoring the encoder power supply

#### Monitoring the encoder power supply

The status of the integrated encoder supplies can be read.

| Bit | Description                               |

|-----|-------------------------------------------|

| 0   | 24 or 5 VDC encoder supply voltage OK     |

| 1   | 24 or 5 VDC encoder supply voltage faulty |

## Information:

The register is described in "Status of encoder supplies" on page 20.

## 3.4 NetTime Technology

NetTime refers to the ability to precisely synchronize and transfer system times between individual components of the controller or network (controller, I/O modules, X2X Link, POWERLINK, etc.).

This allows the moment that events occur to be determined system-wide with microsecond precision. Upcoming events can also be executed precisely at a specified moment.

#### 3.4.1 Time information

Various time information is available in the controller or on the network:

- System time (on the PLC, Automation PC, etc.)

- X2X Link time (for each X2X Link network)

- POWERLINK time (for each POWERLINK network)

- Time data points of I/O modules

The NetTime is based on 32-bit counters, which are increased with microsecond resolution. The sign of the time information changes after 35 min, 47 s, 483 ms and 648  $\mu$ s; an overflow occurs after 71 min, 34 s, 967 ms and 296  $\mu$ s.

The initialization of the times is based on the system time during the startup of the X2X Link, the I/O modules or the POWERLINK interface.

Current time information in the application can also be determined via library AsIOTime.

#### 3.4.1.1 Controller data points

The NetTime I/O data points of the controller are latched to each system clock and made available.

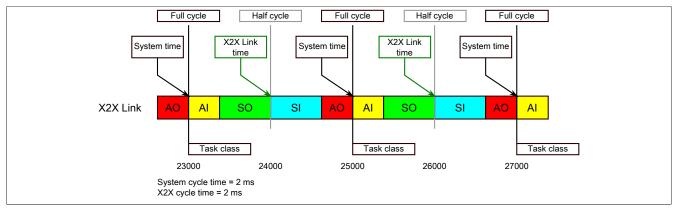

#### 3.4.1.2 X2X Link - Reference time point

The reference time point on the X2X Link network is always calculated at the half cycle of the X2X Link cycle. This results in a difference between the system time and the X2X Link reference time point when the reference time is read out.

In the example above, this results in a difference of 1 ms, i.e. if the system time and X2X Link reference time are compared at time 25000 in the task, then the system time returns the value 25000 and the X2X Link reference time returns the value 24000.

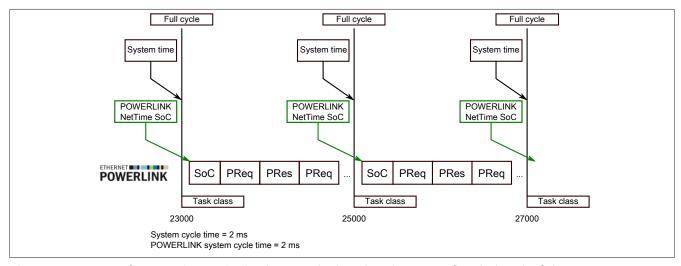

#### 3.4.1.3 POWERLINK - Reference time point

The POWERLINK reference time point is always calculated at the start of cycle (SoC) of the POWERLINK network. The SoC starts 20 µs after the system clock due to the system. This results in the following difference between the system time and the POWERLINK reference time:

POWERLINK reference time = System time - POWERLINK cycle time +  $20 \mu s$

In the example above, this means a difference of 1980  $\mu$ s, i.e. if the system time and POWERLINK reference time are compared at time 25000 in the task, then the system time returns the value 25000 and the POWERLINK reference time returns the value 23020.

## 3.4.1.4 Synchronization of system time/POWERLINK time and I/O module

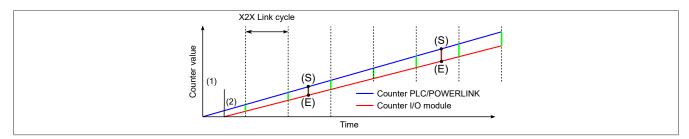

At startup, the internal counters for the controller/POWERLINK (1) and the I/O module (2) start at different times and increase the values with microsecond resolution.

At the beginning of each X2X Link cycle, the controller or POWERLINK network sends time information to the I/O module. The I/O module compares this time information with the module's internal time and forms a difference (green line) between the two times and stores it.

When a NetTime event (E) occurs, the internal module time is read out and corrected with the stored difference value (brown line). This means that the exact system moment (S) of an event can always be determined, even if the counters are not absolutely synchronous.

#### Note

The deviation from the clock signal is strongly exaggerated in the picture as a red line.

#### 3.4.2 Timestamp functions

NetTime-capable modules provide various timestamp functions depending on the scope of functions. If a timestamp event occurs, the module immediately saves the current NetTime. After the respective data is transferred to the controller, including this precise moment, the controller can then evaluate the data using its own NetTime (or system time), if necessary.

For details, see the respective module documentation.

#### 3.4.2.1 Time-based inputs

NetTime Technology can be used to determine the exact moment of a rising edge at an input. The rising and falling edges can also be detected and the duration between 2 events can be determined.

#### Information:

The determined moment always lies in the past.

#### 3.4.2.2 Time-based outputs

NetTime Technology can be used to specify the exact moment of a rising edge on an output. The rising and falling edges can also be specified and a pulse pattern generated from them.

#### Information:

The specified time must always be in the future, and the set X2X Link cycle time must be taken into account for the definition of the moment.

#### 3.4.2.3 Time-based measurements

NetTime Technology can be used to determine the exact moment of a measurement that has taken place. Both the starting and end moment of the measurement can be transmitted.

## 4 Commissioning

## 4.1 Using the module on the bus controller

Function model 254 "Bus controller" is used by default only by non-configurable bus controllers. All other bus controllers can use other registers and functions depending on the fieldbus used.

For detailed information, see section "Additional information - Using I/O modules on the bus controller" in the X20 user's manual (version 3.50 or later).

## 4.1.1 CAN I/O bus controller

The module occupies 1 analog logical slot on CAN I/O.

## **5 Register description**

## 5.1 General data points

In addition to the registers described in the register description, the module has additional general data points. These are not module-specific but contain general information such as serial number and hardware variant.

General data points are described in section "Additional information - General data points" in the X20 System user's manual.

## 5.2 Function model 0 - Standard

| Register     | Name                                                        | Data type      | Read         |         | Write  |         |

|--------------|-------------------------------------------------------------|----------------|--------------|---------|--------|---------|

|              |                                                             |                | Cyclic       | Acyclic | Cyclic | Acyclic |

| Configuratio | n                                                           |                |              |         |        |         |

| 513          | CfO_SIframeGenID                                            | USINT          |              |         |        | •       |

| 642          | CfO_SystemCycleTime                                         | UINT           |              |         |        | •       |

| 769          | CfO_PhylOConfigCh01                                         | USINT          |              |         |        | •       |

| 771          | CfO_PhylOConfigCh02                                         | USINT          |              |         |        | •       |

| 773          | CfO_PhyIOConfigCh03                                         | USINT          |              |         |        | •       |

| 777          | CfO_PhyIOConfigCh04                                         | USINT          |              |         |        | •       |

| 779          | CfO_PhyIOConfigCh05                                         | USINT          |              |         |        | •       |

| 815          | CfO_BWQuitTimeSelChannel7_0                                 | USINT          |              |         |        | •       |

| 820          | CfO_BWQuitTime_0                                            | UDINT          |              |         |        | •       |

| 6145         | CfO_CounterCycleSelect                                      | USINT          |              |         |        | •       |

| 6147         | CfO_CounterMode                                             | USINT          |              |         |        | •       |

| 6149         | CfO_LatchMode                                               | USINT          |              |         |        | •       |

| 6151         | CfO_LatchComparator                                         | USINT          |              |         |        | •       |

| 6159         | CfO_BWCNTEnableMaskChannel7_0                               | USINT          |              |         |        | •       |

| ommunicat    |                                                             |                |              |         |        |         |

| 683          | SDCLifeCount                                                | SINT           | •            |         |        |         |

| 6342         | Encoder01                                                   | INT            | •            |         |        |         |

| 6340         |                                                             | DINT           |              |         |        |         |

| 6310         | Encoder01TimeValid                                          | INT            | •            |         |        |         |

| 6308         |                                                             | DINT           |              |         |        |         |

| 6358         | Encoder01Latch                                              | INT            | •            |         |        |         |

| 6356         |                                                             | DINT           |              |         |        |         |

| 6153         | Encoder commands                                            | USINT          |              |         | •      |         |

|              | Encoder01Reset                                              | Bit 0          |              |         |        |         |

| 007          | Encoder01LatchEnable                                        | Bit 1          |              |         |        |         |

| 927          | Input status of signal lines                                | USINT          | •            |         |        |         |

|              | Encoder01_A                                                 | Bit 0          |              |         |        |         |

|              | Encoder01_B                                                 | Bit 1          |              |         |        |         |

|              | Encoder01_R                                                 | Bit 2          |              |         |        |         |

|              | DigitalInput01                                              | Bit 4          |              |         |        |         |

| 847          | DigitalInput02                                              | Bit 5          |              |         |        |         |

| 841          | Status of signal lines                                      | USINT          | •            |         |        |         |

|              | BW_Channel_A                                                | Bit 0<br>Bit 1 |              |         |        |         |

|              | BW_Channel_B                                                |                |              |         |        |         |

| 011          | BW_Channel_R                                                | Bit 2          |              |         | •      |         |

| 811          | Acknowledging error status of signal lines BW QuitChannel A | USINT<br>Bit 0 |              |         | •      |         |

|              |                                                             |                |              |         |        |         |

|              | BW_QuitChannel_B                                            | Bit 1<br>Bit 2 |              |         |        |         |

| 6326         | BW_QuitChannel_R                                            | INT            | •            |         |        |         |

| 6324         | Encoder01TimeChanged                                        | DINT           | •            |         |        |         |

| 6303         | Encoder01LatchCount                                         | SINT           | •            |         |        |         |

| 843          | Status of encoder supplies                                  | USINT          | <del>`</del> |         |        |         |

| 043          | PowerSupply01                                               | Bit 0          | •            |         |        |         |

|              |                                                             |                |              |         |        |         |

|              | PowerSupply02                                               | Bit 1          |              |         |        | 1       |

## 5.3 Function model 1 - MotionConfiguration

Function model 1 - MotionConfiguration is available starting with hardware upgrade 1.4.0.0.

| Register     | Name                                       | Data type | Read           |  | Write        |   |

|--------------|--------------------------------------------|-----------|----------------|--|--------------|---|

| 1            |                                            |           | Cyclic Acyclic |  | Cyclic Acycl |   |

| Configuratio | n                                          |           |                |  |              |   |

| 513          | CfO_SIframeGenID                           | USINT     |                |  |              | • |

| 642          | CfO_SystemCycleTime                        | UINT      |                |  |              | • |

| 769          | CfO_PhyIOConfigCh01                        | USINT     |                |  |              | • |

| 771          | CfO_PhyIOConfigCh02                        | USINT     |                |  |              | • |

| 773          | CfO_PhyIOConfigCh03                        | USINT     |                |  |              | • |

| 777          | CfO_PhyIOConfigCh04                        | USINT     |                |  |              | • |

| 779          | CfO_PhyIOConfigCh05                        | USINT     |                |  |              | • |

| 815          | CfO_BWQuitTimeSelChannel7_0                | USINT     |                |  |              | • |

| 820          | CfO_BWQuitTime_0                           | UDINT     |                |  |              | • |

| 6145         | CfO_CounterCycleSelect                     | USINT     |                |  |              | • |

| 6147         | CfO_CounterMode                            | USINT     |                |  |              | • |

| 6149         | CfO_LatchMode                              | USINT     |                |  |              | • |

| 6151         | CfO_LatchComparator                        | USINT     |                |  |              | • |

| 6159         | CfO_BWCNTEnableMaskChannel7_0              | USINT     |                |  |              | • |

| Communicat   | ion                                        |           |                |  |              |   |

| 6342         | Encoder01                                  | INT       | •              |  |              |   |

| 6340         |                                            | DINT      |                |  |              |   |

| 6310         | ActTime01                                  | INT       | •              |  |              |   |

| 6308         |                                            | DINT      |                |  |              |   |

| 6358         | RefPulsePos01                              | INT       | •              |  |              |   |

| 6356         | 7                                          | DINT      |                |  |              |   |

| 6153         | Encoder commands                           | USINT     |                |  | •            |   |

|              | Encoder01Reset                             | Bit 0     |                |  |              |   |

| 927          | Input status of signal lines               | USINT     | •              |  |              |   |

|              | Encoder01_A                                | Bit 0     |                |  |              |   |

|              | Encoder01_B                                | Bit 1     |                |  |              |   |

|              | Encoder01 R                                | Bit 2     |                |  |              |   |

|              | DigitalInput01                             | Bit 4     |                |  |              |   |

|              | DigitalInput02                             | Bit 5     |                |  |              |   |

| 847          | Status of signal lines                     | USINT     | •              |  |              |   |

|              | BW_Channel_A                               | Bit 0     |                |  |              |   |

|              | BW_Channel_B                               | Bit 1     |                |  |              |   |

|              | BW_Channel_R                               | Bit 2     |                |  |              |   |

| 811          | Acknowledging error status of signal lines | USINT     |                |  | •            |   |

|              | BW_QuitChannel_A                           | Bit 0     |                |  |              |   |

|              | BW_QuitChannel_B                           | Bit 1     |                |  |              |   |

|              | BW_QuitChannel_R                           | Bit 2     |                |  |              |   |

| 6303         | RefPulseCnt01                              | SINT      | •              |  |              |   |

| 843          | Status of encoder supplies                 | USINT     | •              |  |              |   |

|              | PowerSupply01                              | Bit 0     |                |  |              |   |

|              | PowerSupply02                              | Bit 1     |                |  |              |   |

## 5.4 Function model 254 - Bus controller

| Register     | Offset <sup>1)</sup> | Name                                       | Data type | Re     | ead      | W      | rite     |

|--------------|----------------------|--------------------------------------------|-----------|--------|----------|--------|----------|

|              |                      |                                            |           | Cyclic | Acyclic  | Cyclic | Acyclic  |

| Configuratio | n                    |                                            |           |        |          |        | <u>'</u> |

| 513          | -                    | CfO_SIframeGenID                           | USINT     |        |          |        | •        |

| 642          | -                    | CfO_SystemCycleTime                        | UINT      |        |          |        | •        |

| 769          | -                    | CfO_PhylOConfigCh01                        | USINT     |        |          |        | •        |

| 771          | -                    | CfO_PhyIOConfigCh02                        | USINT     |        |          |        | •        |

| 773          | -                    | CfO_PhylOConfigCh03                        | USINT     |        |          |        | •        |

| 777          | -                    | CfO_PhylOConfigCh04                        | USINT     |        |          |        | •        |

| 779          | -                    | CfO_PhylOConfigCh05                        | USINT     |        |          |        | •        |

| 815          | -                    | CfO_BWQuitTimeSelChannel7_0                | USINT     |        |          |        | •        |

| 820          | -                    | CfO_BWQuitTime_0                           | UDINT     |        |          |        | •        |

| 6145         | -                    | CfO_CounterCycleSelect                     | USINT     |        |          |        | •        |

| 6147         | -                    | CfO_CounterMode                            | USINT     |        |          |        | •        |

| 6149         | -                    | CfO_LatchMode                              | USINT     |        |          |        | •        |

| 6151         | -                    | CfO_LatchComparator                        | USINT     |        |          |        | •        |

| 6159         | -                    | CfO_BWCNTEnableMaskChannel7_0              | USINT     |        |          |        | •        |

| Communicat   | ion                  |                                            |           |        | <u>'</u> |        |          |

| 6342         | 0                    | Encoder01                                  | INT       | •      |          |        |          |

| 6310         | 2                    | Encoder01TimeValid                         | INT       | •      |          |        |          |

| 6358         | 4                    | Encoder01Latch                             | INT       | •      |          |        |          |

| 6153 1       | 1                    | Encoder commands                           | USINT     |        |          | •      |          |

|              |                      | Encoder01Reset                             | Bit 0     |        |          |        |          |

|              |                      | Encoder01LatchEnable                       | Bit 1     |        |          |        |          |

| 927          | 7                    | Input status of signal lines               | USINT     | •      |          |        |          |

|              |                      | Encoder01_A                                | Bit 0     |        |          |        |          |

|              |                      | Encoder01_B                                | Bit 1     |        |          |        |          |

|              |                      | Encoder01_R                                | Bit 2     |        |          |        |          |

|              |                      | DigitalInput01                             | Bit 4     |        |          |        |          |

|              | DigitalInput02       | Bit 5                                      |           |        |          |        |          |

| 847          | 6                    | Status of signal lines                     | USINT     | •      |          |        |          |

|              |                      | BW_Channel_A                               | Bit 0     |        |          |        |          |

|              |                      | BW Channel B                               | Bit 1     |        |          |        |          |

|              |                      | BW_Channel_R                               | Bit 2     |        |          |        |          |

| 811          | 0                    | Acknowledging error status of signal lines | USINT     |        |          | •      |          |

|              | _                    | BW_QuitChannel_A                           | Bit 0     |        |          |        |          |

|              |                      | BW_QuitChannel_B                           | Bit 1     |        |          |        |          |

|              |                      | BW_QuitChannel_R                           | Bit 2     |        |          |        |          |

| 6326         | -                    | Encoder01TimeChanged                       | INT       |        | •        |        |          |

| 6303         | -                    | Encoder01LatchCount                        | SINT      |        | •        |        |          |

| 843          | -                    | Status of encoder supplies                 | USINT     |        | •        |        |          |

|              |                      | PowerSupply01                              | Bit 0     |        |          |        |          |

|              |                      | PowerSupply02                              | Bit 1     |        |          |        |          |

<sup>1)</sup> The offset specifies the position of the register within the CAN object.

## 5.5 Physical configuration

The following registers must be set to the specified constant value for correct physical configuration:

## 5.5.1 Constant register "CfO\_SIframeGenID"

Name:

CfO\_SIframeGenID

| Data type | Value | Information                    |

|-----------|-------|--------------------------------|

| USINT     | 9     | Bus controller default setting |

## 5.5.2 Constant register "CfO\_SystemCycleTime"

Name:

CfO\_SystemCycleTime

Cycle time of encoder acquisition in  $1/8~\mu s$  steps. 1 encoder value is acquired as the counter value per cycle.

| Data type | Value | Information                    |

|-----------|-------|--------------------------------|

| UINT      | 800   | 800 = 100 μs.                  |

|           |       | Bus controller default setting |

## 5.5.3 Constant register "CfO\_PhylOConfigCh0x"

Name:

CfO\_PhylOConfigCh01 to CfO\_PhylOConfigCh05

| Data type | Value | Information                    |

|-----------|-------|--------------------------------|

| USINT     | 0     | Bus controller default setting |

## 5.5.4 Constant register "CfO\_BWQuitTimeSelChannel7\_0"

Name:

$CfO\_BWQuitTimeSelChannel7\_0$

| Data type | Value | Information                    |

|-----------|-------|--------------------------------|

| USINT     | 0     | Bus controller default setting |

## 5.5.5 Constant register "CfO\_CounterCycleSelect"

Name:

CfO\_CounterCycleSelect

| Data type | Value | Information                    |

|-----------|-------|--------------------------------|

| USINT     | 2     | Bus controller default setting |

## 5.5.6 Constant register "CfO\_CounterMode"

Name:

CfO\_CounterMode

| Data type | Value | Information                    |

|-----------|-------|--------------------------------|

| USINT     | 3     | Bus controller default setting |

## 5.6 General communication

## 5.6.1 Counter for verifying the data frame

Name:

**SDCLifeCount**

The 8-bit counter register is needed for the SDC software package. It is incremented with the system clock to allow the SDC to check the validity of the data frame.

| Data type | Values      |

|-----------|-------------|

| SINT      | -128 to 127 |

## 5.6.2 Input status of signal lines

Name:

Encoder01 A

Encoder01 B

Encoder01 R

DigitalInput01 to DigitalInput02

This register displays the input status of the signal lines from the encoder and the digital inputs.

| Data type | Value              |  |

|-----------|--------------------|--|

| USINT     | See bit structure. |  |

#### Bit structure:

| Bit   | Name           | Value | Information                     |

|-------|----------------|-------|---------------------------------|

| 0     | Encoder01_A    | 0/1   | Input state of encoder signal A |

| 1     | Encoder01_B    | 0/1   | Input state of encoder signal B |

| 2     | Encoder01_R    | 0/1   | Input state of encoder signal R |

| 3     | Reserved       | 0     |                                 |

| 4     | DigitalInput01 | 0/1   | Input state - Digital input 1   |

| 5     | DigitalInput02 | 0/1   | Input state - Digital input 2   |

| 6 - 7 | Reserved       | 0     |                                 |

## 5.6.3 Status of encoder supplies

Name:

PowerSupply01 to PowerSupply02

This register shows the status of the integrated encoder supplies. A faulty encoder power supply is displayed as a warning.

| Data type | Value              |

|-----------|--------------------|

| USINT     | See bit structure. |

#### Bit structure:

| Bit | Name          | Value | Information                        |

|-----|---------------|-------|------------------------------------|

| 0   | PowerSupply01 | 0     | 24 VDC encoder power supply OK     |

|     |               | 1     | 24 VDC encoder power supply faulty |

| 1   | PowerSupply02 | 0     | 5 VDC encoder power supply OK      |

|     |               | 1     | 5 VDC encoder power supply faulty  |

| 2-7 | Reserved      | -     |                                    |

## 5.7 Counter and latch

#### 5.7.1 Encoder commands

Name:

Encoder01Command

This register can be used to

- 1) reset the counter value. The counter is kept at zero until this command is reset.

- 2) enable the latch procedure. If the latch configuration is valid and matches the hardware signals, then this activation causes the counter value to be saved in the latch register.

| Data type | Value              |

|-----------|--------------------|

| USINT     | See bit structure. |

Bit structure with function model 0 - Standard:

| Bit   | Name                 | Value | Information            |

|-------|----------------------|-------|------------------------|

| 0     | Encoder01Reset       | 0     | Do not reset           |

|       |                      | 1     | Set encoder value to 0 |

| 1     | Encoder01LatchEnable | 0     | Do not latch           |

|       |                      | 1     | Latch                  |

| 2 - 7 | Reserved             | 0     |                        |

Bit structure with function model 1 - MotionConfiguration:

#### Information:

The latch procedure is always enabled in function model 1 - MotionConfiguration.

|   | Bit | Name           | Value | Information            |

|---|-----|----------------|-------|------------------------|

| ĺ | 0   | Encoder01Reset | 0     | Do not reset           |

| ĺ |     |                | 1     | Set encoder value to 0 |

| Ì | 1-7 | Reserved       | 0     |                        |

#### 5.7.2 Setting the latch mode

Name:

CfO\_LatchMode

This register is used to set the latch mode. For details, see "Latching counter values" on page 8.

A changed counter state on "Encoder01LatchCount" on page 22 indicates that the latch procedure has been performed. The counter value is stored in the latch register "Encoder01Latch" on page 22.

Description for function model 0 - Standard:

| Data type | Values | Information                                                             |  |

|-----------|--------|-------------------------------------------------------------------------|--|

| USINT     | 0      | One-time (single-shot) latch procedure (bus controller default setting) |  |

|           | 1      | Continuous latch procedure                                              |  |

Description for function model 1 - MotionConfiguration:

| Data type | Values | Information                                                  |  |

|-----------|--------|--------------------------------------------------------------|--|

| USINT     | 1      | Continuous latch procedure                                   |  |

|           |        | The register is always written with "1" in function model 1. |  |

#### 5.7.3 Signal channels for triggering latch procedure

Name:

CfO\_LatchComparator

This register defines the inputs and their level for triggering the latch procedure. For details, see "Latching counter values" on page 8.

| Data type | Values                 | Bus controller default setting |

|-----------|------------------------|--------------------------------|

| USINT     | See the bit structure. | 0                              |

#### Bit structure:

| Bit | Name                                            | Value | Information                               |

|-----|-------------------------------------------------|-------|-------------------------------------------|

| 0   | Defines signal level for encoder signal A       | 0     | Low (bus controller default setting)      |

|     |                                                 | 1     | High                                      |

| 1   | Defines signal level for encoder signal B       | 0     | Low (bus controller default setting)      |

|     |                                                 | 1     | High                                      |

| 2   | Defines signal level for encoder signal R       | 0     | Low (bus controller default setting)      |

|     |                                                 | 1     | High                                      |

| 3   | Defines signal level for digital input 1        | 0     | Low (bus controller default setting)      |

|     |                                                 | 1     | High                                      |

| 4   | Use encoder signal A to trigger latch procedure | 0     | Disabled (bus controller default setting) |

|     |                                                 | 1     | Latch function linked to encoder signal A |

| 5   | Use encoder signal B to trigger latch procedure | 0     | Disabled (bus controller default setting) |

|     |                                                 | 1     | Latch function linked to encoder signal B |

| 6   | Use encoder signal R to trigger latch procedure | 0     | Disabled (bus controller default setting) |

|     |                                                 | 1     | Latch function linked to encoder signal R |

| 7   | Use digital input 1 to trigger latch procedure  | 0     | Disabled (bus controller default setting) |

|     |                                                 | 1     | Latch function linked to digital input 1  |

#### 5.7.4 Display of the counter state

Name:

Encoder01

The counter state of the incremental encoder is displayed as a 16 or 32-bit counter value. Only the 16-bit value is available in the bus controller function model.

| Data type          | Value                            |

|--------------------|----------------------------------|

| INT                | -32768 to 32767                  |

| DINT <sup>1)</sup> | -2.147.483.648 bis 2.147.483.647 |

<sup>1)</sup> Only configurable in the function models Standard and MotionConfiguration

#### 5.7.5 Counter value at the time of the last latch

Name:

Encoder01Latch ... Designation in function model 0 - Standard RefPulsePos01 ... Designation in function model 1 - MotionConfiguration

The counter value at the time of the last latch is displayed as a 16 or 32-bit value. Only the 16-bit value is available in the bus controller function model.

| Data type          | Value                            |

|--------------------|----------------------------------|

| INT                | -32768 to 32767                  |

| DINT <sup>1)</sup> | -2.147.483.648 bis 2.147.483.647 |

<sup>1)</sup> Only configurable in the function models Standard and MotionConfiguration

#### 5.7.6 Counter value of latch event

Name:

Encoder01LatchCount ... Designation in function model 0 - Standard RefPulseCnt01 ... Designation in function model 1 - MotionConfiguration

The latch events are counted and stored in a cyclic 8-bit counter. This counter is incremented with each latch event, thereby indicating a new occurrence. The new latched counter value is stored in the respective latch register.

| Data type | Value       |

|-----------|-------------|

| SINT      | -128 to 127 |

## 5.8 Signal line error states

When they occur, the error states are latched and remain so until they have been acknowledged. With pending or unacknowledged errors, the counter and time registers are not updated.

#### 5.8.1 Enabling error monitoring for the signal lines

Name:

CfO\_BWCNTEnableMaskChannel7\_0

With this register, error monitoring must be enabled for each signal channel individually. Any errors that occur are reported in the error status registers "BW\_Channel\_x" on page 23.

| Data type | Value              | Bus controller default setting |

|-----------|--------------------|--------------------------------|

| USINT     | See bit structure. | 7                              |

#### Bit structure:

| Bit   | Name                                       | Value | Information                                                                  |

|-------|--------------------------------------------|-------|------------------------------------------------------------------------------|

| 0     | Enable error monitoring for signal A lines | 0     | Error monitoring - Encoder Signal A disabled                                 |

|       |                                            | 1     | Error monitoring - Encoder signal A enabled (bus controller default setting) |

| 1     | Enable error monitoring for signal B lines | 0     | Error monitoring - Encoder Signal B disabled                                 |

|       |                                            | 1     | Error monitoring - Encoder signal B enabled (bus controller default setting) |

| 2     | Enable error monitoring for signal R lines | 0     | Error monitoring - Encoder Signal R disabled                                 |

|       |                                            | 1     | Error monitoring - Encoder signal R enabled (bus controller default setting) |

| 3 - 7 | Reserved                                   | 0     |                                                                              |

### 5.8.2 Timing for automatic error acknowledgment

Name:

CfO\_BWQuitTime\_0

With this register, additional automatic acknowledgment of the error state can be switched on using a time setting.

| Data type | Value              | Information                            |  |

|-----------|--------------------|----------------------------------------|--|

| UDINT     | 0                  | No automatic acknowledgment.           |  |

|           |                    | Bus controller default setting         |  |

|           | 1 to 2.147.483.647 | Time for automatic acknowledgment [µs] |  |

#### 5.8.3 Status of signal lines

Name:

BW\_Channel\_A

BW\_Channel\_B

BW\_Channel\_R

The error states of the signal lines from the encoder are mapped in this register.

| Data type | Value              |

|-----------|--------------------|

| USINT     | See bit structure. |

#### Bit structure:

| Bit   | Name         | Value | Information                                       |

|-------|--------------|-------|---------------------------------------------------|

| 0     | BW_Channel_A | 0     | No error in encoder signal A                      |

|       |              | 1     | Open line, short circuit or voltage level too low |

| 1     | BW_Channel_B | 0     | No error in encoder signal B                      |

|       |              | 1     | Open line, short circuit or voltage level too low |

| 2     | BW_Channel_R | 0     | No error in encoder signal R                      |

|       |              | 1     | Open line, short circuit or voltage level too low |

| 3 - 7 | Reserved     | 0     |                                                   |

#### 5.8.4 Acknowledging error status of signal lines

Name:

BW\_QuitChannel\_A BW\_QuitChannel\_B BW QuitChannel R

This register can be used to acknowledge latched error states.

| Data type | Value              |

|-----------|--------------------|

| USINT     | See bit structure. |

#### Bit structure:

| Bit   | Name             | Value | Information                                       |

|-------|------------------|-------|---------------------------------------------------|

| 0     | BW_QuitChannel_A | 0     | No acknowledgment                                 |

|       |                  | 1     | Acknowledgment of error status - Encoder signal A |

| 1     | BW_QuitChannel_B | 0     | No acknowledgment                                 |

|       |                  | 1     | Acknowledgment of error status - Encoder signal B |

| 2     | BW_QuitChannel_R | 0     | No acknowledgment                                 |

|       |                  | 1     | Acknowledgment of error status - Encoder signal R |

| 3 - 7 | Reserved         | 0     |                                                   |

#### 5.9 NetTime

#### 5.9.1 NetTime of the last valid counter value

#### Name:

Encoder01TimeValid ... Designation in function model 0 - Standard ActTime01 ... Designation in function model 1 - MotionConfiguration

The NetTime of the last valid counter value is the time of the last valid counter value recorded on the module (see register "Cfo\_SystemCycleTime" on page 18). The user is able to determine the validity of the counter value by evaluating its age in the program. This means that the module and error status bits do not have to be checked additionally to determine the validity of the value.

The NetTime of the last valid counter value that was read is displayed as a 16 or 32-bit value. Only the 16-bit value is available in the bus controller function model.

For additional information about NetTime and timestamps, see "NetTime Technology" on page 12.

| Data type          | Value            | Information   |

|--------------------|------------------|---------------|

| INT                | -32768 to 32767  | NetTime in µs |

| DINT <sup>1)</sup> | -2.147.483.648   |               |

|                    | to 2.147.483.647 |               |

<sup>1)</sup> Only configurable in the function models Standard and MotionConfiguration

#### 5.9.2 NetTime of the last counter value change

Name:

Encoder01TimeChanged

For slow X2X Link cycles, the NetTime of the last counter value change can be used to determine the speed more accurately.

The NetTime of the last counter value change is displayed as a 16 or 32-bit value. Only the 16-bit value is available in the bus controller function model.

For additional information about NetTime and timestamps, see "NetTime Technology" on page 12.

| Data type          | Value            | Information   |

|--------------------|------------------|---------------|

| INT                | -32768 to 32767  | NetTime in μs |

| DINT <sup>1)</sup> | -2.147.483.648   |               |

|                    | to 2.147.483.647 |               |

<sup>1)</sup> Can only be configured in the standard function model

## 5.10 Minimum cycle time

The minimum cycle time defines how far the bus cycle can be reduced without causing a communication error or impaired functionality. It should be noted that very fast cycles decrease the idle time available for handling monitoring, diagnostics and acyclic commands.

| Minimum cycle time |

|--------------------|

| 150 μs             |

## 5.11 Minimum I/O update time

The minimum I/O update time defines how far the bus cycle can be reduced while still allowing an I/O update to take place in each cycle.

| Minimum I/O update time |

|-------------------------|

| 150 μs                  |