# X20AI2632

Data sheet 3.21 (June 2025)

#### **Publishing information**

B&R Industrial Automation GmbH B&R Strasse 1 5142 Eggelsberg Austria

Telephone: +43 7748 6586-0

Fax: +43 7748 6586-26

office@br-automation.com

#### Disclaimer

All information in this document is current as of its creation. The contents of this document are subject to change without notice. B&R Industrial Automation GmbH assumes unlimited liability in particular for technical or editorial errors in this document only (i) in the event of gross negligence or (ii) for culpably inflicted personal injury. Beyond that, liability is excluded to the extent permitted by law. Liability in cases in which the law stipulates mandatory unlimited liability (such as product liability) remains unaffected. Liability for indirect damage, consequential damage, business interruption, loss of profit or loss of information and data is excluded, in particular for damage that is directly or indirectly attributable to the delivery, performance and use of this material.

B&R Industrial Automation GmbH notes that the software and hardware designations and brand names of the respective companies used in this document are subject to general trademark, brand or patent protection.

Hardware and software from third-party suppliers referenced in this document is subject exclusively to the respective terms of use of these third-party providers. B&R Industrial Automation GmbH assumes no liability in this regard. Any recommendations made by B&R Industrial Automation GmbH are not contractual content, but merely non-binding information for which no liability is assumed. When using hardware and software from third-party suppliers, the relevant user documentation of these third-party suppliers must additionally be consulted and, in particular, the safety guidelines and technical specifications contained therein must be observed. The compatibility of the products from B&R Industrial Automation GmbH described in this document with hardware and software from third-party suppliers is not contractual content unless this has been separately agreed in individual cases; in this respect, warranty for such compatibility is excluded in any case, and it is the sole responsibility of the customer to verify this compatibility in advance.

1247782281222-3.21

## 1 General information

## 1.1 Other applicable documents

For additional and supplementary information, see the following documents.

## Other applicable documents

| Document name | Title                    |

|---------------|--------------------------|

| MAX20         | X20 System user's manual |

## 1.2 Order data

| Order number | Short description                                                                                                                      | Figure                                  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

|              | Analog input modules                                                                                                                   |                                         |

| X20AI2632    | X20 analog input module, 2 inputs, ±10 V or 0 to 20 mA, 16-bit converter resolution, configurable input filter, oscilloscope functions | 33                                      |

|              | Required accessories                                                                                                                   | 1 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 |

|              | Bus modules                                                                                                                            | X20 F                                   |

| X20BM11      | X20 bus module, 24 VDC keyed, internal I/O power supply connected through                                                              | ) E                                     |

| X20BM15      | X20 bus module, with node number switch, 24 VDC keyed, internal I/O power supply connected through                                     |                                         |

|              | Terminal blocks                                                                                                                        |                                         |

| X20TB06      | X20 terminal block, 6-pin, 24 VDC keyed                                                                                                |                                         |

| X20TB12      | X20 terminal block, 12-pin, 24 VDC keyed                                                                                               |                                         |

Table 1: X20AI2632 - Order data

## 1.3 Module description

The module is equipped with 2 inputs with 16-bit digital converter resolution and very fast conversion time. It is possible to select between the current and voltage signal using different terminals.

This module is designed for X20 6-pin terminal blocks. If needed (e.g. for logistical reasons), the 12-pin terminal block can also be used.

#### **Functions:**

- Scaling

- Filtering

- · Error monitoring

- · Analysis functions

#### Scaling

The A/D converter data can optionally be scaled by the user to ensure the greatest possible flexibility.

#### Input filter

An input filter can be configured for each individual analog input.

#### **Error monitoring**

The input signal is monitored for range overshoot, synchronization errors and invalid sampling cycles. User-defined limit values can also be defined.

#### **Analysis functions**

In addition to sampling the analog input signal, the values determined can also be analyzed:

- · Limit value analysis

- Recording the sampled values

- Trace

# 2 Technical description

## 2.1 Technical data

| Order number                                                     | X20Al2632                                                                                                                        |

|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Short description                                                |                                                                                                                                  |

| I/O module                                                       | 2 analog inputs ±10 V or 0 to 20 mA                                                                                              |

| General information                                              |                                                                                                                                  |

| B&R ID code                                                      | 0x1BA0                                                                                                                           |

| Status indicators                                                | I/O function per channel, operating state, module status                                                                         |

| Diagnostics                                                      |                                                                                                                                  |

| Module run/error                                                 | Yes, using LED status indicator and software                                                                                     |

| Inputs                                                           | Yes, using LED status indicator and software                                                                                     |

| Channel type                                                     | Yes, using software                                                                                                              |

| Power consumption                                                |                                                                                                                                  |

| Bus                                                              | 0.01 W                                                                                                                           |

| Internal I/O                                                     | 1.2 W <sup>1)</sup>                                                                                                              |

| Additional power dissipation caused by actuators (resistive) [W] | -                                                                                                                                |

| Certifications                                                   |                                                                                                                                  |

| CE                                                               | Yes                                                                                                                              |

| UKCA                                                             | Yes                                                                                                                              |

| ATEX                                                             | Zone 2, II 3G Ex nA nC IIA T5 Gc<br>IP20, Ta (see X20 user's manual)<br>FTZÚ 09 ATEX 0083X                                       |

| UL                                                               | cULus E115267<br>Industrial control equipment                                                                                    |

| HazLoc                                                           | cCSAus 244665 Process control equipment for hazardous locations Class I, Division 2, Groups ABCD, T5                             |

| DNV                                                              | Temperature: <b>B</b> (0 to 55°C) Humidity: <b>B</b> (up to 100%) Vibration: <b>B</b> (4 g) EMC: <b>B</b> (bridge and open deck) |

| CCS                                                              | Yes                                                                                                                              |

| LR                                                               | ENV1                                                                                                                             |

| KR                                                               | Yes                                                                                                                              |

| ABS                                                              | Yes                                                                                                                              |

| BV                                                               | EC33B  Temperature: 5 - 55°C  Vibration: 4 g  EMC: Bridge and open deck                                                          |

| KC                                                               | Yes                                                                                                                              |

| Analog inputs                                                    | HOVen One 20 and the different terms in Learness time.                                                                           |

| Input                                                            | ±10 V or 0 to 20 mA, via different terminal connections                                                                          |

| Input type                                                       | Differential input                                                                                                               |

| Digital converter resolution                                     | 11F bis                                                                                                                          |

| Voltage                                                          | ±15-bit                                                                                                                          |

| Current Conversion time                                          | 15-bit                                                                                                                           |

| Conversion time Output format                                    | 50 μs for all inputs                                                                                                             |

| Output format Output format                                      | INT                                                                                                                              |

| Voltage                                                          | INT 0x8001 - 0x7FFF / 1 LSB = 0x0001 = 305.176 μV                                                                                |

| Current                                                          | INT 0x8001 - 0x7FFF / 1 LSB = 0x0001 = 305.176 μV  INT 0x0000 - 0x7FFF / 1 LSB = 0x0001 = 610.352 nA                             |

| Input impedance in signal range                                  | IIN I UXUUUU - UX1FFF / 1 L3D - UXUUU1 = 010.332 IIA                                                                             |

| Voltage                                                          | 20 ΜΩ                                                                                                                            |

| Current                                                          |                                                                                                                                  |

| Load                                                             | <u>-</u>                                                                                                                         |

| Voltage                                                          | <u>.</u>                                                                                                                         |

| Current                                                          | - <400 Ω                                                                                                                         |

| Input protection                                                 | Protection against wiring with supply voltage                                                                                    |

| Permissible input signal                                         | Trocection against wining with supply voltage                                                                                    |

| Voltage                                                          | Max. ±30 V                                                                                                                       |

| Current                                                          | Max. ±50 mA                                                                                                                      |

Table 2: X20AI2632 - Technical data

## **Technical description**

| Order number                               | X20Al2632                                                                                                  |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Output of digital value during overload    |                                                                                                            |

| Undershoot                                 |                                                                                                            |

| Voltage                                    | 0x8001                                                                                                     |

| Current                                    | 0x0000                                                                                                     |

| Overshoot                                  |                                                                                                            |

| Voltage                                    | 0x7FFF                                                                                                     |

| Current                                    | 0x7FFF                                                                                                     |

| Conversion procedure                       | SAR                                                                                                        |

| Input filter                               | Hardware - Third-order low-pass filter / cutoff frequency 10 kHz                                           |

| Max. error                                 |                                                                                                            |

| Voltage                                    |                                                                                                            |

| Gain                                       | 0.08% 2)                                                                                                   |

| Offset                                     | 0.01% 3)                                                                                                   |

| Current                                    |                                                                                                            |

| Gain                                       | 0.08% 2)                                                                                                   |

| Offset                                     | 0.02% 4)                                                                                                   |

| Max. gain drift                            |                                                                                                            |

| Voltage                                    | 0.01%/°C <sup>2)</sup>                                                                                     |

| Current                                    | 0.01%/°C ²)                                                                                                |

| Max. offset drift                          | ,                                                                                                          |

| Voltage                                    | 0.001%/°C <sup>3)</sup>                                                                                    |

| Current                                    | 0.002%/°C <sup>4)</sup>                                                                                    |

| Common-mode rejection                      |                                                                                                            |

| DC                                         | 70 dB                                                                                                      |

| 50 Hz                                      | 70 dB                                                                                                      |

| Common-mode range                          | ±12 V                                                                                                      |

| Crosstalk between channels                 | <-70 dB                                                                                                    |

| Nonlinearity                               |                                                                                                            |

| Voltage                                    | <0.01% 3)                                                                                                  |

| Current                                    | <0.015% 4)                                                                                                 |

| Insulation voltage between channel and bus | 500 V <sub>eff</sub>                                                                                       |

| Electrical properties                      |                                                                                                            |

| Electrical isolation                       | Channel isolated from bus                                                                                  |

|                                            | Channel not isolated from channel                                                                          |

| Operating conditions                       |                                                                                                            |

| Mounting orientation                       |                                                                                                            |

| Horizontal                                 | Yes                                                                                                        |

| Vertical                                   | Yes                                                                                                        |

| Installation elevation above sea level     |                                                                                                            |

| 0 to 2000 m                                | No limitation                                                                                              |

| >2000 m                                    | Reduction of ambient temperature by 0.5°C per 100 m                                                        |

| Degree of protection per EN 60529          | IP20                                                                                                       |

| Ambient conditions                         |                                                                                                            |

| Temperature                                |                                                                                                            |

| Operation                                  |                                                                                                            |

| Horizontal mounting orientation            | -25 to 60°C                                                                                                |

| Vertical mounting orientation              | -25 to 50°C                                                                                                |

| Derating                                   | -                                                                                                          |

| Storage                                    | -40 to 85°C                                                                                                |

| Transport                                  | -40 to 85°C                                                                                                |

| Relative humidity                          |                                                                                                            |

| Operation                                  | 5 to 95%, non-condensing                                                                                   |

| Storage                                    | 5 to 95%, non-condensing                                                                                   |

| Transport                                  | 5 to 95%, non-condensing                                                                                   |

| Mechanical properties                      |                                                                                                            |

| Note                                       |                                                                                                            |

|                                            | Order 1x terminal block X20TB06 or X20TB12 separately.                                                     |

|                                            | Order 1x terminal block X20TB06 or X20TB12 separately. Order 1x bus module X20BM11 separately.  12.5+02 mm |

Table 2: X20AI2632 - Technical data

- To reduce power dissipation, B&R recommends bridging unused inputs on the terminals or configuring them as current signals. Based on the current measured value.

Based on the 20 V measurement range.

- 2)

- Based on the 20 mA measurement range.

## 2.2 LED status indicators

For a description of the various operating modes, see section "Additional information - Diagnostic LEDs" in the X20 system user's manual.

| Figure                                  | LED           | Color     | Status       | Description                                       |

|-----------------------------------------|---------------|-----------|--------------|---------------------------------------------------|

|                                         | r             | Green Off |              | No power to module                                |

|                                         |               |           | Single flash | RESET mode                                        |

|                                         |               |           | Double flash | BOOT mode (during firmware update) <sup>1)</sup>  |

|                                         |               |           | Blinking     | PREOPERATIONAL mode                               |

|                                         |               |           | On           | RUN mode                                          |

| 7 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 | е             |           | Off          | No power to module or everything OK               |

| Ň                                       |               |           | On           | Error or reset status                             |

| 4                                       |               |           | Double flash | System error:                                     |

| 20                                      |               |           |              | Violation of the scan time                        |

| ×                                       |               |           |              | Synchronization error                             |

| The second second                       | 1-2 Green Off |           | Off          | Open line <sup>2)</sup> or sensor is disconnected |

|                                         |               |           | On           | Analog/digital converter running, value OK        |

<sup>1)</sup> Depending on the configuration, a firmware update can take up to several minutes.

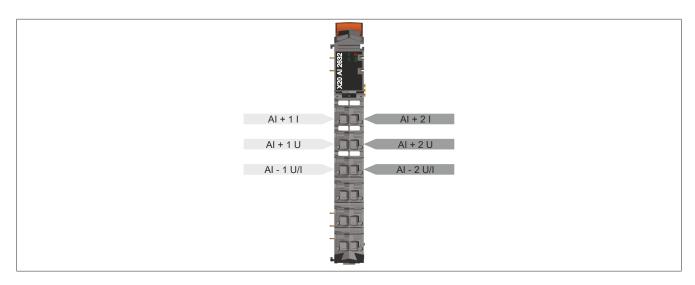

## 2.3 Pinout

<sup>2)</sup> Open line detection only possible when measuring voltage.

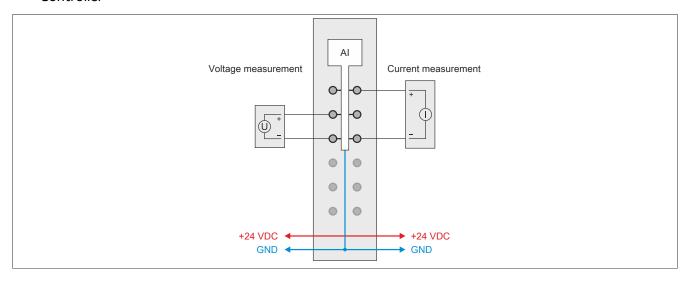

## 2.4 Connection example

To prevent disturbances, the following modules must be separated by at least one module:

- Bus receiver X20BR9300

- Supply module X20PS3300/X20PS3310

- Supply module X20PS9400/X20PS9402

- Power supply module X20PS9600/X20PS9602

- Controller

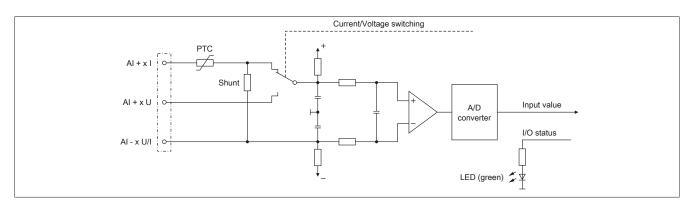

## 2.5 Input circuit diagram

## **3 Function description**

## 3.1 Analog inputs

The module is equipped with analog inputs with connected 16-bit A/D converters. Each of the inputs can be configured separately for either voltage or current input for the following ranges:

• Permissible voltage: ±10 V

· Permissible current: 0 to 20 mA

Configuration must take place in addition to using suitable terminals.

## Information:

The register is described in "Channel configuration" on page 18.

#### 3.1.1 Scaling

The A/D converter data can optionally be scaled by the user. The following additional registers are available for this:

- Gain = ku

- Offset = du

#### Scaling calculation:

Scaled value = k \* A/C value + d

Gain k = k<sub>Calibration</sub> \* ku

Offset  $d = d_{Calibration} + du$

The value must be limited since it can exceed the 16-bit constraints. If the application requires a restriction of the range of values, the user can define custom limit values. These are also used for the module's error statistics.

## Information:

Within the module, 32-bit numbers are used for the limit values. A limit value violation can therefore also be detected if the permissible range of values of -32768 to 32767 has been defined.

## Information:

The registers are described in "User-defined scaling" on page 19.

#### 3.1.2 Filtering

If filtering has been enabled, the basic data of the A/D converters is filtered per channel. The filter order and respective cutoff frequency of the low-pass filter can be configured for this.

Internal filter orders greater than 1 are implemented as cascaded first-order filters.

#### Calculating the cutoff frequency of an nth-order filter:

Cutoff frequency = Cutoff frequency<sub>n</sub> /  $((2 ^ (1 / n) - 1) ^ 0.5)$

#### Approximate calculation

```

yn = a * xn + b * y(n-1)

a = Sampling time<sub>Sec</sub> / (Sampling time<sub>Sec</sub> + 1 / (2 Pi * Cutoff frequency<sub>Hz</sub>))

```

b = 1 - a

## Information:

Since low-pass filtering takes place using an approximation procedure with fixed-point arithmetic, there are discrepancies to the effective cutoff frequency that depend on the sampling cycle and filter sequence.

## Information:

The registers are described in "Filtering" on page 18.

## 3.2 Error monitoring

There are various counter registers in the module that can be used to record the occurrence of certain errors.

The counters in these registers follow the rules of the event error counter, i.e. each occurrence or reset of an error increases the counter value. The last bit of the counter indicates the error state:

- Last bit = 1 → Error pending

- Last bit = 0 → No error

The following errors are monitored:

#### Synchronization error

This error shows how often the conversion task was triggered more than 5  $\mu$ s after the previous X2X cycle.

#### Invalid sampling cycles

This error indicates a cycle time violation. The error occurs if the conversion task triggers a sampling task before the last sampling cycle has been completed.

#### Workspace overshoots

This indicates errors outside the maximum possible measurement range of the module.

#### · Range undershoots

This indicates range undershoots below the value set as "Minimum limit value".

## Range overshoots

This indicates range overshoots above the value set as "Maximum limit value".

#### Overshoots and undershoots

These counters are only operated if the static error counters are enabled in the channel configuration.

## Information:

The registers are described in "Error monitoring and counters" on page 20.

## 3.3 Analysis functions

In addition to sampling the analog input signal, this module can also be used to perform additional analysis of the values obtained.

#### 3.3.1 Limit value analysis

Limit value analysis must be enabled for the desired channel. The sampled value of the channel is then compared with the minimum and maximum values stored internally within the module. If a new measurement period is triggered, the values from the last measuring period can be read out from the registers provided for this purpose.

If limit value analysis has been enabled for a channel, the sampled minimum and maximum values are latched within the module. A measurement period can be triggered via the control byte. If the corresponding configured edge is generated by the application, the limit values of the last measurement period are displayed and the internal latch registers are reset.

#### Information:

The registers are described in "Limit values" on page 24.

## 3.3.2 Recording the sampled values

If the recording of sampled values has been enabled for a channel, the sampled values are also recorded in a module-internal FIFO memory. When the configured event occurs, the contents of the FIFO memory are transmitted to the application.

#### Information:

Recording of sampled values can only be used if the module is operated on an X2X master that is a type SG4 controller.

The analog signal is sampled in 2 steps.

#### Conversion task

The A/D converter digitalizes the inputs signals for the enabled inputs once per conversion cycle. Then the results are available internally in the module. To ensure that this process is executed without delays, the corresponding task will be handled with very high priority.

The timespan needed for conversion results from the set sampling time.

#### Processing task

The converted A/D converter values are further processed according to the user settings (filtering, scaling, limit values, error statistics, min/max analysis, hysteresis comparison). The task for this process has low priority. The timespan needed for further processing depends on the configured functions and is the second portion of the sampling time.

#### Cycle time violation

In normal operation, further processing is triggered after each conversion. The conversion and sampling tasks run synchronous to one another. If the predefined sampling time is not sufficient to convert all enabled channels and complete the configured functions, a cycle time violation occurs.

#### Information:

The register is described in "Sampling time" on page 18.

#### 3.3.3 Trace

If the module is operated on a type SG4 controller, the digitized input values can be recorded by the module. Module monitoring must be enabled to use measured value recording.

Recording must be enabled for the desired channel. The enable bits can then control the recording at runtime. The sampled values are recorded in the module's internal FIFO memory.

If the previously defined state occurs on the channel, the contents of the FIFO memory are transmitted to the application. Whether the FIFO memory continued to be filled depends on how recording is configured.

#### Information:

The trace mechanism cannot be used if the module is operated behind a bus controller, but only when it is directly connected to the controller.

#### Information:

The registers are described in "Trace" on page 25.

Library "AsIOTrc" is used to read out the trace data.

Register "TraceChannelEnable" on page 25 determines the structure of the trace buffer.

Example of the structure of the trace buffer:

Both channels of the module are used in this example. Both channels are sampled per trigger and stored one after the other in the trace buffer.

| Channel sequence |

|------------------|

| 1                |

| 2                |

| 1                |

| 2                |

| 1                |

| 2                |

|                  |

The length of the trace buffer is determined with registers "TraceTriggerStart" on page 29 and "TraceTriggerStop" on page 29.

Parameter "Number of trace buffers" must be defined in Automation Studio in order to configure the trace function block.

12

#### 3.3.3.1 Comparator for trigger conditions

In order to adapt the trace as closely as possible to the requirements of the application, the trace function can also be controlled using the comparator. Threshold values (hysteresis) can be defined within the permitted range of values to do so. 2 status bits are then generated for each enabled channel:

#### InRange bit

The InRange status is "1" if the measured value falls within the defined limits.

The InRange status is "0" if the measured value falls outside the defined limits.

#### · Threshold value bit

The threshold value bit is "1" if the measured value exceeds the upper threshold value.

The threshold value bit is "0" if the measured value falls below the lower threshold value.

The InRange and threshold bits of all channels are combined in the least significant byte of register CompStateCollection. In addition, the states of the previous sampling are stored in the high-order byte.

The 4 status messages of each channel can be linked via a link mask using AND or OR operators according to the following logic and used as triggers for recordings.

```

delta = (Current_HysteresisStatus ^ NominalValues)// Difference between current status and preset

cond = delta & Selected_HysteresisStatusBits// Eliminate irrelevant status messages

cond = Selected_HysteresisStatusBits (Current_HysteresisStatus ^ NominalValues)

if((0==(cond & ~LogicalOperators)) &&

(0!=(~cond & LogicalOperators))) {=> Generate trigger event}

```

Selected\_HysteresisStatusBits Current\_HysteresisStatus Nominal values Logical operators Corresponds to register: cfgComp\_EnableMask CompStateCollection cfgComp\_NominalState cfgComp\_ConditionTypeMask

#### Information:

The registers are described in "Comparator for trigger conditions" on page 27.

#### 3.3.3.2 Recording measured values

The module has 16 kB available for the trace. The limitation of the FIFO memory means that a maximum of 8192 analog values can be recorded. The memory is divided evenly between the enabled channels. The actual maximum number of possible recordings therefore depends on the number of channels registered for the trace:

1 channel enabled: Maximum 8192 recordings

2 channels enabled: Maximum 4096 recordings per channel

#### **Time-shifted recording**

If the recording should be defined with a time offset to the trigger, additional conditions can be defined for shifting the start and stop time.

#### Information:

The registers are described in "Time-offset trace" on page 29.

## 4 Commissioning

## 4.1 Using the module on the bus controller

Function model 254 "Bus controller" is used by default only by non-configurable bus controllers. All other bus controllers can use other registers and functions depending on the fieldbus used.

For detailed information, see section "Additional information - Using I/O modules on the bus controller" in the X20 user's manual (version 3.50 or later).

## 4.1.1 CAN I/O bus controller

The module occupies 1 analog logical slot on CAN I/O.

## **5 Register description**

## 5.1 General data points

In addition to the registers described in the register description, the module has additional general data points. These are not module-specific but contain general information such as serial number and hardware variant.

General data points are described in section "Additional information - General data points" in the X20 System user's manual.

## 5.2 Function model 0 - default

| Register    | Name                                               | Data type | Re     | ead      | W      | rite    |

|-------------|----------------------------------------------------|-----------|--------|----------|--------|---------|

|             |                                                    |           | Cyclic | Acyclic  | Cyclic | Acyclic |

| onfiguratio | n - Frame size                                     |           |        |          |        |         |

| -           | AsynSize                                           | -         |        |          |        |         |

| onfiguratio |                                                    |           |        |          |        |         |

| 257         | ConfigOutput01 (channel configuration)             | USINT     |        |          |        | •       |

| 289         | ConfigOutput06 (channel configuration)             | USINT     |        |          |        | •       |

|             | Sampling time                                      | •         |        |          |        |         |

| 390         | ConfigOutput24 (sampling time)                     | UINT      |        |          |        | •       |

|             | Filtering                                          | ,         |        |          |        |         |

| 259         | ConfigOutput26 (filter order)                      | USINT     |        |          |        | •       |

| 291         | ConfigOutput28 (filter order)                      | USINT     |        |          |        | •       |

| 262         | ConfigOutput27 (filter cutoff frequency)           | UINT      |        |          |        | •       |

| 294         | ConfigOutput29 (filter cutoff frequency)           | UINT      |        |          |        | •       |

|             | Scaling                                            |           |        | 1        | l .    |         |

| 276         | ConfigOutput04 (user-defined gain)                 | DINT      |        |          |        | •       |

| 308         | ConfigOutput09 (user-defined gain)                 | DINT      |        |          |        | •       |

| 284         | ConfigOutput05 (user-defined offset)               | DINT      |        |          |        | •       |

| 316         | ConfigOutput10 (user-defined offset)               | DINT      |        |          |        | •       |

| 520         | User-defined limit values                          |           |        |          |        |         |

| 266         | ConfigOutput02 (minimum limit value)               | UINT      |        |          |        | •       |

| 298         | ConfigOutput07 (minimum limit value)               | UINT      |        |          |        | •       |

| 270         | ConfigOutput03 (maximum limit value)               | UINT      |        |          |        | •       |

| 302         | ConfigOutput08 (maximum limit value)               | UINT      |        |          |        | •       |

| ommunicat   |                                                    | Olivi     |        |          |        |         |

| 0           | AnalogInput01                                      | INT       | •      |          |        |         |

| 4           | Analoginput02                                      | INT       | •      |          |        |         |

| 650         | 9 .                                                | UINT      |        | •        |        |         |

| 050         | SampleCycleCounter                                 | UINI      |        |          |        |         |

| C 41        | Error monitoring and counters                      | LICINIT   | •      | 1        |        | 1       |

| 641         | Channel status                                     | USINT     | •      |          |        |         |

|             | Channel010K                                        | Bit 0     |        |          |        |         |

|             | Channel02OK                                        | Bit 1     |        |          |        |         |

|             | SyncStatus                                         | Bit 6     |        |          |        |         |

|             | ConvertionCycle                                    | Bit 7     |        |          |        |         |

| 654         | SampleCycleViolationErrorCounter                   | UINT      |        | •        |        |         |

| 658         | SynchronizationViolationErrorCounter               | UINT      |        | •        |        |         |

| 2097        | Range undershoot and overshoot                     | USINT     | •      |          |        |         |

|             | Channel01underflow                                 | Bit 0     |        |          |        |         |

|             | Channel02underflow                                 | Bit 1     |        |          |        |         |

|             | Channel01overflow                                  | Bit 4     |        |          |        |         |

|             | Channel02overflow                                  | Bit 5     |        |          |        |         |

| 2099        | Workspace overshoot                                | USINT     | •      |          |        |         |

|             | Channel01outofrange                                | Bit 0     |        |          |        |         |

|             | Channel02outofrange                                | Bit 1     |        |          |        |         |

| 518         | Ch01OutOfRange                                     | UINT      |        | •        |        |         |

| 550         | Ch02OutOfRange                                     | UINT      |        | •        |        |         |

| 522         | Ch01Underflow                                      | UINT      |        | •        |        |         |

| 554         | Ch02Underflow                                      | UINT      |        | •        |        |         |

| 526         | Ch01Overflow                                       | UINT      |        | •        |        |         |

| 558         | Ch02Overflow                                       | UINT      |        | •        |        |         |

|             | nalysis functions                                  |           |        | <u> </u> |        | ·       |

| 133         | ConfigOutput21 (trigger condition on falling edge) | USINT     |        |          |        | •       |

| 135         | ConfigOutput22 (trigger condition on rising edge)  | USINT     |        |          |        | •       |

## **Register description**

| Register | Name                            | Data type | Read   |         |        | Write   |  |

|----------|---------------------------------|-----------|--------|---------|--------|---------|--|

|          |                                 |           | Cyclic | Acyclic | Cyclic | Acyclic |  |

| 129      | Analysis control byte           | USINT     |        |         | •      |         |  |

|          | TraceTrigger01                  | Bit 0     |        |         |        |         |  |

|          | MinMaxStart01                   | Bit 4     |        |         |        |         |  |

|          | MinMaxStart02                   | Bit 5     |        |         |        |         |  |

| 129      | Analysis status byte            | USINT     | •      |         |        |         |  |

|          | MinMaxStart01Readback           | Bit 4     |        |         |        |         |  |

|          | MinMaxStart02Readback           | Bit 5     |        |         |        |         |  |

|          | Limit values                    |           |        |         |        |         |  |

| 530      | MinInput01                      | INT       | •      |         |        |         |  |

| 562      | MinInput02                      | INT       | •      |         |        |         |  |

| 534      | MaxInput01                      | INT       | •      |         |        |         |  |

| 566      | MaxInput02                      | INT       | •      |         |        |         |  |

| 538      | Ch01MinMaxLatchCounter          | UINT      |        | •       |        |         |  |

| 570      | Ch02MinMaxLatchCounter          | UINT      |        | •       |        |         |  |

|          | Trace configuration             |           |        |         |        | _       |  |

| 1026     | TraceChannelEnable              | USINT     |        |         |        | •       |  |

| 1030     | TraceSampleDepth                | UINT      |        |         |        | •       |  |

| 4157     | ConfigOutput25 (trace priority) | USINT     |        |         |        | •       |  |

| 1037     | Enabling the trace function     | USINT     |        |         | •      |         |  |

|          | TraceEnable01                   | Bit 0     | 1      |         |        |         |  |

| 1089     | Trace status                    | USINT     | •      |         |        |         |  |

|          | TraceEnabled                    | Bit 0     |        |         |        |         |  |

|          | TraceWriteActive                | Bit 2     |        |         |        |         |  |

|          | TraceReadActive                 | Bit 3     |        |         |        |         |  |

|          | ReadyForTrigger                 | Bit 4     |        |         |        |         |  |

|          | TriggerActive                   | Bit 5     |        |         |        |         |  |

|          | TraceOK                         | Bit 6     |        |         |        |         |  |

|          | TraceError                      | Bit 7     |        |         |        |         |  |

| 1094     | FreeBufferSize                  | UINT      | •      |         |        |         |  |

| 1098     | TriggerCount                    | UINT      | •      |         |        |         |  |

| 1102     | TriggerFailCount                | UINT      | •      |         |        |         |  |

|          | Comparator                      |           |        |         |        |         |  |

| 450      | cfgComp_LowLimitCh01            | INT       |        |         | (•)    | •       |  |

| 458      | cfgComp_LowLimitCh02            | INT       |        |         | (•)    | •       |  |

| 454      | cfgComp_HighLimitCh01           | INT       |        |         | (•)    | •       |  |

| 462      | cfgComp_HighLimitCh02           | INT       |        |         | (•)    | •       |  |

| 662      | CompStateCollection             | UINT      | •      |         |        |         |  |

| 490      | cfgComp_NominalState            | UINT      |        |         |        | •       |  |

| 482      | cfgComp_EnableMask              | UINT      |        |         |        | •       |  |

| 486      | cfgComp_ConditionTypeMask       | UINT      |        |         |        | •       |  |

|          | Time-offset trace               |           |        | 1       |        | 1       |  |

| 1042     | TraceTriggerStart               | INT       |        |         |        | •       |  |

| 1046     | TraceTriggerStop                | UINT      |        |         |        | •       |  |

## 5.3 Function model 254 - Bus controller

| Register           | Offset1)        | Name                                                | Data type | Re     | ad      | W      | rite    |

|--------------------|-----------------|-----------------------------------------------------|-----------|--------|---------|--------|---------|

|                    |                 |                                                     |           | Cyclic | Acyclic | Cyclic | Acyclic |

| Configuration      | - Frame size    |                                                     |           |        | ı       | T      |         |

| -<br>Configuration | -               | AsynSize                                            | -         |        |         |        |         |

| 257                | _               | ConfigOutput01 (channel configuration)              | USINT     |        | I       | I      | •       |

| 289                | _               | ConfigOutput06 (channel configuration)              | USINT     |        |         |        | •       |

|                    | Sampling tim    |                                                     | 03        |        |         |        |         |

| 390                | -               | ConfigOutput24 (sampling time)                      | UINT      |        |         |        | •       |

|                    | Filtering       | The State of the State of                           |           |        | I.      | I.     |         |

| 259                | -               | ConfigOutput26 (filter order)                       | USINT     |        |         |        | •       |

| 291                | -               | ConfigOutput28 (filter order)                       | USINT     |        |         |        | •       |

| 262                | -               | ConfigOutput27 (filter cutoff frequency)            | UINT      |        |         |        | •       |

| 294                | -               | ConfigOutput29 (filter cutoff frequency)            | UINT      |        |         |        | •       |

|                    | Scaling         |                                                     |           |        |         |        |         |

| 276                | -               | ConfigOutput04 (user-defined gain)                  | DINT      |        |         |        | •       |

| 308                | -               | ConfigOutput09 (user-defined gain)                  | DINT      |        |         |        | •       |

| 284                | -               | ConfigOutput05 (user-defined offset)                | DINT      |        |         |        | •       |

| 316                | -               | ConfigOutput10 (user-defined offset)                | DINT      |        |         |        | •       |

|                    | User-defined    |                                                     |           |        |         | 1      |         |

| 266                | -               | ConfigOutput02 (minimum limit value)                | UINT      |        |         |        | •       |

| 298                | -               | ConfigOutput07 (minimum limit value)                | UINT      |        |         |        | •       |

| 270                | -               | ConfigOutput03 (maximum limit value)                | UINT      |        |         |        | •       |

| 302                | -               | ConfigOutput08 (maximum limit value)                | UINT      |        |         |        | •       |

| Communication      |                 | Analogianut01                                       | INIT      |        |         |        |         |

| 0<br>4             | 2               | AnalogInput01 AnalogInput02                         | INT       | •      |         |        |         |

| 650                | 2               | SampleCycleCounter                                  | UINT      |        | •       |        |         |

| 650                | Error monito    | pring and counters                                  | UINT      |        |         |        |         |

| 641                | _               | Channel status                                      | USINT     |        |         |        |         |

| 041                | _               | Channel010K                                         | Bit 0     |        |         |        |         |

|                    |                 | Channel020K                                         | Bit 1     |        |         |        |         |

|                    |                 | SyncStatus                                          | Bit 6     |        |         |        |         |

|                    |                 | ConvertionCycle                                     | Bit 7     |        |         |        |         |

| 654                | -               | SampleCycleViolationErrorCounter                    | UINT      |        | •       |        |         |

| 658                | -               | SynchronizationViolationErrorCounter                | UINT      |        | •       |        |         |

| 2097               | -               | Range undershoot and overshoot                      | USINT     |        | •       |        |         |

|                    |                 | Channel01underflow                                  | Bit 0     |        |         |        |         |

|                    |                 | Channel02underflow                                  | Bit 1     |        |         |        |         |

|                    |                 | Channel01overflow                                   | Bit 4     |        |         |        |         |

|                    |                 | Channel02overflow                                   | Bit 5     |        |         |        |         |

| 2099               | -               | Workspace overshoot                                 | USINT     |        | •       |        |         |

|                    |                 | Channel01outofrange                                 | Bit 0     |        |         |        |         |

|                    |                 | Channel02outofrange                                 | Bit 1     |        |         |        |         |

| 518                | -               | Ch01OutOfRange                                      | UINT      |        | •       |        |         |

| 550                | -               | Ch02OutOfRange                                      | UINT      |        | •       |        |         |

| 522                | -               | Ch01Underflow                                       | UINT      |        | •       |        |         |

| 554                | -               | Ch02Underflow                                       | UINT      |        | •       |        |         |

| 526                | -               | Ch01Overflow                                        | UINT      |        | •       |        |         |

| 558                | -               | Ch02Overflow                                        | UINT      |        | •       |        |         |

|                    | alysis function |                                                     | 11000     |        |         |        |         |

| 133                | -               | ConfigOutput21 (trigger condition on falling        | USINT     |        |         |        | •       |

| 135                | _               | edge)  ConfigOutput22 (trigger condition on rising) | USINT     |        |         |        | •       |

| 133                | _               | edge)                                               | CSINI     |        |         |        |         |

| 129                | -               | Analysis control byte                               | USINT     |        |         |        | •       |

|                    |                 | TraceTrigger01                                      | Bit 0     |        |         |        |         |

|                    |                 | MinMaxStart01                                       | Bit 4     |        |         |        |         |

|                    |                 | MinMaxStart02                                       | Bit 5     |        |         |        |         |

| 129                | -               | Analysis status byte                                | USINT     |        | •       |        |         |

|                    |                 | MinMaxStart01Readback                               | Bit 4     |        |         |        |         |

|                    |                 | MinMaxStart02Readback                               | Bit 5     |        |         |        |         |

|                    | Limit values    |                                                     |           |        |         |        |         |

| 530                | -               | MinInput01                                          | INT       |        | •       |        |         |

| 562                | -               | MinInput02                                          | INT       |        | •       |        |         |

| 534                | -               | MaxInput01                                          | INT       | -      | •       |        |         |

| 566                | -               | MaxInput02                                          | INT       |        | •       |        |         |

|                    | 1               |                                                     | LUNIT     |        | •       |        |         |

| 538<br>570         | -               | Ch01MinMaxLatchCounter Ch02MinMaxLatchCounter       | UINT      |        | _ •     |        |         |

<sup>1)</sup> The offset specifies the position of the register within the CAN object.

## 5.4 Configuration

## 5.4.1 Channel configuration

Name:

ConfigOutput01 for channel 1 ConfigOutput06 for channel 2

The individual inputs for processing the current or voltage signal are configured in these registers. This configuration must be made in addition to using suitable terminals.

Filtering, analysis and error monitoring (bits 4 to 6) can only be used if the channel is enabled (bit 7 = 0).

| Data type | Values                 | Bus controller default setting |

|-----------|------------------------|--------------------------------|

| USINT     | See the bit structure. | 0                              |

#### Bit structure:

| Bit   | Description                     | Value | Information                                                   |

|-------|---------------------------------|-------|---------------------------------------------------------------|

| 0     | Terminal selector               | 0     | Voltage terminal for ±10 VDC (bus controller default setting) |

|       |                                 | 1     | Current terminal for 0 to 20 mA                               |

| 1     | Gain selector                   | 0     | Voltage ±10 VDC (bus controller default setting)              |

|       |                                 | 1     | Current 0 to 20 mA                                            |

| 2 - 3 | Reserved                        | -     |                                                               |

| 4     | Filtering active                | 0     | Inactive (bus controller default setting)                     |

|       |                                 | 1     | Active                                                        |

| 5     | Minimum/Maximum analysis active | 0     | Inactive (bus controller default setting)                     |

|       |                                 | 1     | Active                                                        |

| 6     | Error monitoring active         | 0     | Inactive (bus controller default setting)                     |

|       |                                 | 1     | Active                                                        |

| 7     | Enables channel                 | 0     | Channel enabled (bus controller default setting)              |

|       |                                 | 1     | Channel disabled                                              |

#### 5.4.2 Sampling time

Name:

ConfigOutput24

The sampling time is set to  $\mu$ s in this register. This makes it possible to improve the sampling cycle (resolution = 1  $\mu$ s). The lowest configurable cycle time is 50  $\mu$ s.

| Data type | Value        | Information                         |

|-----------|--------------|-------------------------------------|

| UINT      | 50 to 10,000 | Bus controller default setting: 100 |

#### Information:

Values that are too low for the cycle time will result in cycle time violations.

#### 5.4.3 Filtering

#### 5.4.3.1 Filter order

Name:

ConfigOutput26 for channel 1 ConfigOutput28 for channel 2

The filter order is specified in this register. The "Filter cutoff frequency" on page 19 register is used to configure the respective cutoff frequency of the filter.

| Data type | Value  | Information                       |  |

|-----------|--------|-----------------------------------|--|

| USINT     | 1 to 4 | Bus controller default setting: 0 |  |

#### 5.4.3.2 Filter cutoff frequency

Name:

ConfigOutput27 for channel 1 ConfigOutput29 for channel 2

The cutoff frequency of the respective filter is configured in these registers.

| Data type | Value       | Information                       |  |

|-----------|-------------|-----------------------------------|--|

| UINT      | 1 to 65,535 | Cutoff frequency in hertz.        |  |

|           |             | Bus controller default setting: 0 |  |

## Information:

The highest cutoff frequency is limited by the Nyquist Shannon sampling theorem (based on the sampling cycle time). The system does not check for violations of this sampling theorem.

#### 5.4.4 User-defined scaling

## 5.4.4.1 User-defined gain

Name:

ConfigOutput04 for channel 1 ConfigOutput09 for channel 2

The user-defined gain for the A/D converter data of the respective physical channel can be specified in these registers.

The value 65536 (0x10000) corresponds to a gain of 1.

| Data type | Values           | Information                           |  |

|-----------|------------------|---------------------------------------|--|

| DINT      | -2,147,483,648   | Bus controller default setting: 65536 |  |

|           | to 2,147,483,647 |                                       |  |

#### 5.4.4.2 User-defined offset

Name:

ConfigOutput05 for channel 1

ConfigOutput10 for channel 2

The user-defined offset for the A/D converter data of the respective physical channel can be specified in this register.

The value 65536 (0x10000) corresponds to an offset of 1.

| Data type | Values           | Information                       |  |

|-----------|------------------|-----------------------------------|--|

| DINT      | -2,147,483,648   | Bus controller default setting: 0 |  |

|           | to 2,147,483,647 |                                   |  |

#### 5.4.5 User-defined limit values

## 5.4.5.1 Minimum limit value

Name:

ConfigOutput02 for channel 1

ConfigOutput07 for channel 2

The minimum limit value is configured in this register. This limit value is also used for the undershoot error statistics (see register "Ch0xUnderflow" on page 22).

| Data type | Values          | Information                            |  |

|-----------|-----------------|----------------------------------------|--|

| INT       | -32768 to 32767 | Bus controller default setting: -32768 |  |

#### 5.4.5.2 Maximum limit value

Name:

ConfigOutput03 for channel 1 ConfigOutput08 for channel 2

The maximum limit value is configured in this register. This limit value is also used for the overflow error statistics (see register "Ch0xOverflow" on page 22).

| Data type | Values          | Information                           |  |

|-----------|-----------------|---------------------------------------|--|

| INT       | -32767 to 32767 | Bus controller default setting: 32767 |  |

#### 5.5 Communication - General

The analog inputs of the module convert the current or voltage values with a resolution of 16 bits. The information can be used by the application via the registers described here.

## 5.5.1 Analog inputs

Name:

AnalogInput01 to AnalogInput02

The analog input value is mapped in this register depending on the configured operating mode.

| Data type | Value             | Input signal              |  |

|-----------|-------------------|---------------------------|--|

| INT       | -32,768 to 32,767 | Voltage signal ±10 VDC    |  |

|           | 0 to 32,767       | Current signal 0 to 20 mA |  |

#### 5.5.2 Sampling cycle counter

Name:

SampleCycleCounter

The number of times the input signal has been sampled is provided in this register.

| Data type | Values     |

|-----------|------------|

| UINT      | 0 to 65535 |

## 5.6 Error monitoring and counters

#### 5.6.1 Channel status

Name:

Channel01OK to Channel02OK

SyncStatus

ConvertionCycle

This register collects error messages synchronously with the network cycle. Temporary error states that were registered in a conversion cycle remain active for at least 2 network cycles. In order to receive detailed error information, the corresponding error counters and X2X network events should also be observed.

| Data type | Values                 |

|-----------|------------------------|

| USINT     | See the bit structure. |

#### Bit structure:

| Bit   | Description                   | Value | Information      |

|-------|-------------------------------|-------|------------------|

| 0     | Channel010K                   | 0     | OK               |

|       |                               | 1     | Errors           |

| 1     | Channel02OK                   | 0     | OK               |

|       |                               | 1     | Errors           |

| 2 - 5 | Reserved                      | -     |                  |

| 6     | SyncStatus <sup>1)</sup>      | 0     | OK               |

|       |                               | 1     | Not synchronized |

| 7     | ConvertionCycle <sup>2)</sup> | 0     | OK               |

|       |                               | 1     | Errors           |

<sup>1)</sup> Identical to bit 0 of the registers "SynchronizationViolationErrorCounter" on page 21.

<sup>2)</sup> Identical to bit 0 of the registers "SampleCycleViolationErrorCounter" on page 22.

#### 5.6.2 Workspace overshoot

#### Name:

Channel01outofrange to Channel02outofrange

This register indicates whether the input value overshoots the module's maximum measurement range. The individual bits in this register are identical to the value of the lowest bit of register "Ch0xOutOfRange" on page 22.

| Data type | Values                 |

|-----------|------------------------|

| USINT     | See the bit structure. |

#### Bit structure:

| Bit   | Description         | Value | Information                                 |

|-------|---------------------|-------|---------------------------------------------|

| 0     | Channel01outofrange | 0     | No error                                    |

|       |                     | 1     | Working range violation (pos.) of channel 1 |

| 1     | Channel02outofrange | 0     | No error                                    |

|       |                     | 1     | Working range violation (pos.) of channel 2 |

| 2 - 7 | Reserved            | -     |                                             |

## 5.6.3 Range undershoot and overshoot

#### Name:

Channel01underflow to Channel02underflow Channel01overflow to Channel02overflow

This register indicates whether the limit values defined by registers "Minimum limit value" on page 19 and "Maximum limit value" on page 20 have been overshot or undershot. The individual bits in this register are identical to the value of the lowest bit of registers "Ch0xUnderflow" on page 22 and "Ch0xOverflow" on page 22.

| Data type | Values                 |

|-----------|------------------------|

| USINT     | See the bit structure. |

#### Bit structure:

| Bit   | Description        | Value | Information                        |

|-------|--------------------|-------|------------------------------------|

| 0     | Channel01underflow | 0     | No error                           |

|       |                    | 1     | Range exceeded (.neg) on channel 1 |

| 1     | Channel02underflow | 0     | No error                           |

|       |                    | 1     | Range exceeded (.neg) on channel 2 |

| 2 - 3 | Reserved           | -     |                                    |

| 4     | Channel01overflow  | 0     | No error                           |

|       |                    | 1     | Range exceeded (.pos) on channel 1 |

| 5     | Channel02overflow  | 0     | No error                           |

|       |                    | 1     | Range exceeded (.pos) on channel 2 |

| 6 - 7 | Reserved           | -     |                                    |

## 5.6.4 Counter for synchronization errors

#### Name

SynchronizationViolationErrorCounter

This register counts how often the conversion task was triggered more than 5 µs after the next-coming X2X cycle. In this case, the module is considered being no longer synchronized with X2X Link.

| Data type | Value      | Information <sup>1)</sup> |

|-----------|------------|---------------------------|

| UINT      | 0 to 65535 | Counter value             |

|           | 0 to 1     | Bit 0: Error status       |

1) For details, see "Error monitoring" on page 10.

#### 5.6.5 Counter for faulty sampling cycles

Name:

SampleCycleViolationErrorCounter

This register is used to indicate the number of cycle time violations that have occurred thus far. A cycle time violation occurs if the conversion tasks initiates a sampling task before the last sampling cycle has finished. See "Recording the sampled values" on page 11.

| Data type | Value      | Information <sup>1)</sup> |

|-----------|------------|---------------------------|

| UINT      | 0 to 65535 | Counter value             |

|           | 0 to 1     | Bit 0: Error status       |

<sup>1)</sup> For details, see "Error monitoring" on page 10.

#### **5.6.6 Counter for workspace overshoots**

Name:

Ch01OutOfRange to Ch02OutOfRange

This register indicates errors outside the maximum possible measurement range of the module. These errors result in a final deflection of the A/D converter.

| Data type | Value      | Information <sup>1)</sup> |

|-----------|------------|---------------------------|

| UINT      | 0 to 65535 | Counter value             |

|           | 0 to 1     | Bit 0: Error status       |

<sup>1)</sup> For details, see "Error monitoring" on page 10.

## 5.6.7 Counter for range exceeded violations (neg.)

Name:

Ch01Underflow to Ch02Underflow

This register indicates the range undershoots below the value set in register "Minimum limit value" on page 19.

| Data type | Value      | Information <sup>1)</sup> |

|-----------|------------|---------------------------|

| UINT      | 0 to 65535 | Counter value             |

|           | 0 to 1     | Bit 0: Error status       |

<sup>1)</sup> For details, see "Error monitoring" on page 10.

#### 5.6.8 Counter for range exceeded violations (pos.)

Name:

Ch01Overflow to Ch02Overflow

This register indicates the range overshoots above the value set in register "Maximum limit value" on page 20.

| Data type | Value      | Information <sup>1)</sup> |

|-----------|------------|---------------------------|

| UINT      | 0 to 65535 | Counter value             |

|           | 0 to 1     | Bit 0: Error status       |

<sup>1)</sup> For details, see "Error monitoring" on page 10.

## 5.7 Analysis functions

In addition to sampling the analog input signal, this module can also be used to perform additional analysis of the values obtained.

## 5.7.1 Trigger condition on falling edge

Name:

ConfigOutput21

This register can be used to configure whether the falling edge is used to trigger the trace and determine the input value in register "Analysis control byte" on page 24.

| Data type | Values                 | Bus controller default setting |

|-----------|------------------------|--------------------------------|

| USINT     | See the bit structure. | 0                              |

#### Bit structure:

| Bit   | Description    | Value | Information                                       |

|-------|----------------|-------|---------------------------------------------------|

| 0     | TraceTrigger01 | 0     | No trigger (bus controller default setting)       |

|       |                | 1     | Falling edge active as trigger                    |

| 1 - 3 | Reserved       | -     |                                                   |

| 4     | MinMaxStart01  | 0     | No determination (bus controller default setting) |

|       |                | 1     | Falling edge determines input value of channel 1  |

| 5     | MinMaxStart02  | 0     | No determination (bus controller default setting) |

|       |                | 1     | Falling edge determines input value of channel 2  |

| 6 - 7 | Reserved       | 0     |                                                   |

## 5.7.2 Trigger condition on rising edge

Name:

ConfigOutput22

This register can be used to configure whether the rising edge is used to trigger the trace and determine the input value in register "Analysis control byte" on page 24.

| Data type | Values                 | Bus controller default setting |

|-----------|------------------------|--------------------------------|